From WikiChip

Difference between revisions of "ti/tms1000/tms1098"

(+title) |

|||

| (4 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

{{ti title|TMS1098}} | {{ti title|TMS1098}} | ||

| + | {{chip | ||

| + | |chip type=microcontroller | ||

| + | |name=TMS1098 | ||

| + | |image=tms1098jlp_se2.jpg | ||

| + | |designer=Texas Instruments | ||

| + | |manufacturer=Texas Instruments | ||

| + | |model number=TMS1098 | ||

| + | |first announced=1974 | ||

| + | |first launched=1974 | ||

| + | |family=TMS1000 | ||

| + | |frequency=400 kHz | ||

| + | |microarch=TMS1000 | ||

| + | |process=8 µm | ||

| + | |word size=4 bit | ||

| + | |max memory=32 KiB | ||

| + | |average power=110 mW | ||

| + | |v core=15 V | ||

| + | |package module 1={{packages/pdip-64}} | ||

| + | |package module 2={{packages/cdip-64}} | ||

| + | }} | ||

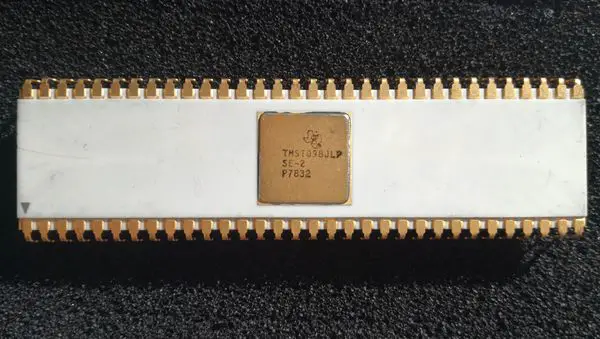

The TMS1098JL is a ROM-less version of TMS1000-TMS1200. It has 64 pins, 128x4 bits of RAM, 8 bits of "O" parallel latched data outputs and 16 "R" individually addressed output latches. The package pin count is 64. | The TMS1098JL is a ROM-less version of TMS1000-TMS1200. It has 64 pins, 128x4 bits of RAM, 8 bits of "O" parallel latched data outputs and 16 "R" individually addressed output latches. The package pin count is 64. | ||

| Line 6: | Line 26: | ||

This ROM-less version addresses 2048 x 8 bits on an external memory (EPROM). | This ROM-less version addresses 2048 x 8 bits on an external memory (EPROM). | ||

| − | [[File:tms1098jlp_se2.jpg|border|600px|The TMS 1098 JLP SE-2]] | + | |

| + | :[[File:tms1098jlp_se2.jpg|border|600px|The TMS 1098 JLP SE-2]] | ||

Latest revision as of 13:56, 13 December 2017

| Edit Values | |||||

| TMS1098 | |||||

| |||||

| General Info | |||||

| Designer | Texas Instruments | ||||

| Manufacturer | Texas Instruments | ||||

| Model Number | TMS1098 | ||||

| Introduction | 1974 (announced) 1974 (launched) | ||||

| General Specs | |||||

| Family | TMS1000 | ||||

| Frequency | 400 kHz | ||||

| Microarchitecture | |||||

| Microarchitecture | TMS1000 | ||||

| Process | 8 µm | ||||

| Word Size | 4 bit | ||||

| Max Memory | 32 KiB | ||||

| Electrical | |||||

| Power dissipation (average) | 110 mW | ||||

| Vcore | 15 V | ||||

| Packaging | |||||

| |||||

| |||||

The TMS1098JL is a ROM-less version of TMS1000-TMS1200. It has 64 pins, 128x4 bits of RAM, 8 bits of "O" parallel latched data outputs and 16 "R" individually addressed output latches. The package pin count is 64.

The maximum-rated voltage is 20 V and the typical dissipation is 110mW (per power supply of 15 V).

This ROM-less version addresses 2048 x 8 bits on an external memory (EPROM).

Facts about "TMS1098 - TI"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | TMS1098 - TI#package + |

| base frequency | 0.4 MHz (4.0e-4 GHz, 400 kHz) + |

| core voltage | 15 V (150 dV, 1,500 cV, 15,000 mV) + |

| designer | Texas Instruments + |

| family | TMS1000 + |

| first announced | 1974 + |

| first launched | 1974 + |

| full page name | ti/tms1000/tms1098 + |

| instance of | microcontroller + |

| ldate | 1974 + |

| main image |  + + |

| manufacturer | Texas Instruments + |

| max memory | 0.0313 MiB (32 KiB, 32,768 B, 3.051758e-5 GiB, 2.980232e-8 TiB) + |

| microarchitecture | TMS1000 + |

| model number | TMS1098 + |

| name | TMS1098 + |

| package | PDIP-64 + and CDIP-64 + |

| power dissipation (average) | 0.11 W (110 mW, 1.4751e-4 hp, 1.1e-4 kW) + |

| process | 8,000 nm (8 μm, 0.008 mm) + |

| word size | 4 bit (0.5 octets, 1 nibbles) + |