| (19 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{pezy title|PEZY-SC}} | {{pezy title|PEZY-SC}} | ||

| − | {{ | + | {{chip |

|name=PEZY-SC | |name=PEZY-SC | ||

| − | |image=pezy sc. | + | |image=pezy-sc (front).png |

| − | |||

|designer=PEZY | |designer=PEZY | ||

|manufacturer=TSMC | |manufacturer=TSMC | ||

| Line 10: | Line 9: | ||

|first announced=2013 | |first announced=2013 | ||

|first launched=September, 2014 | |first launched=September, 2014 | ||

| + | |family=PEZY-SCx | ||

|frequency=733.33 MHz | |frequency=733.33 MHz | ||

|process=28 nm | |process=28 nm | ||

| + | |transistors=3,730,000,000 | ||

|technology=CMOS | |technology=CMOS | ||

|die area=411.6 mm² | |die area=411.6 mm² | ||

|die length=19.5 mm | |die length=19.5 mm | ||

|die width=21.1 mm | |die width=21.1 mm | ||

| − | |core count= | + | |core count=1,024 |

| + | |thread count=8,192 | ||

|power=100 W | |power=100 W | ||

| − | | | + | |average power=70 W |

| − | | | + | |v core=1.0 V |

| − | + | |package module 1={{packages/pezy/fcbga-2112}} | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |package | ||

| − | |||

| − | |||

}} | }} | ||

| − | '''PEZY-SC''' ('''PEZY Super Computer''') is second generation [[many-core microprocessor]] developed by [[PEZY]] in 2014. | + | '''PEZY-SC''' ('''PEZY Super Computer''') is a second generation [[many-core microprocessor]] developed by [[PEZY]] and introduced in 2014. This chip, which operates at 733 MHz, incorporates 1,024 cores dissipating 100 W. The PEZY-SC powers the [[ZettaScaler]]-1.x series of supercomputers. The PEZY-SC is used in a number of [[TOP500]] & [[Green500]] supercomputers as the world's most efficient supercomputers. |

== Overview == | == Overview == | ||

{{see also|pezy/pezy-1|l1=PEZY-1}} | {{see also|pezy/pezy-1|l1=PEZY-1}} | ||

| − | The PEZY-SC (SC for "Super Computer") is [[PEZY]]'s second generation microprocessors which builds upon the {{pezy|PEZY-1}}. The chip contains exactly twice as many cores and incorporates a large amount of cache including 8 MB of L3$. | + | The PEZY-SC (SC for "Super Computer") is [[PEZY]]'s second generation microprocessors which builds upon the {{pezy|PEZY-1}}. The chip contains exactly twice as many cores and incorporates a large amount of cache including 8 MB of L3$. The chip contains 2 {{armh|ARM926}} cores ({{arm|ARMv5TEJ}}) along with 1,024 simpler cores supporting 8-way [[simultaneous multithreading|SMT]] for a total of 8,192 [[logical core|threads]]. Operating at 733 MHz, the processor has a peak performance of 3.0 [[TFLOPS]] (single-precision) and 1.5 TFLOPS (double-precision). PEZY-SC was designed using 580 million gates and manufactured on [[28 nm process|TSMC's 28HPC+]]. |

| + | {{#set: | ||

| + | | peak flops (single-precision) = {{#expr:733333333 * 4 * 1024}} FLOPS | ||

| + | | peak flops (double-precision) = {{#expr:733333333 * 2 * 1024}} FLOPS | ||

| + | }} | ||

| + | The chip has a peak power dissipation of 100 W with a typical power consumption of 70 W which consists of 10 W [[static power|leakage]] + 60 W [[dynamic power|dynamic]]. | ||

In June of 2015, PEZY-SC-based [[supercomputer]]s took all top 3 spots on the [[Green500]] listing as the 3 most efficient supercomputers. PEZY-SC powers [[Shoubu]] (1,181,952 cores, ? kW, 605.624 TFlop/s [[Linpack]] Rmax), and [[Suiren Blue]] (262,656 cores, 40.86 kW, 247.752 TFlop/s Linpack Rmax), and [[Suiren]] (328,480 cores, 48.90 kW, 271.782 TFlop/s Linpack Rmax) supercomputers (ranked 1, 2, and 3 respectively). | In June of 2015, PEZY-SC-based [[supercomputer]]s took all top 3 spots on the [[Green500]] listing as the 3 most efficient supercomputers. PEZY-SC powers [[Shoubu]] (1,181,952 cores, ? kW, 605.624 TFlop/s [[Linpack]] Rmax), and [[Suiren Blue]] (262,656 cores, 40.86 kW, 247.752 TFlop/s Linpack Rmax), and [[Suiren]] (328,480 cores, 48.90 kW, 271.782 TFlop/s Linpack Rmax) supercomputers (ranked 1, 2, and 3 respectively). | ||

== Architecture == | == Architecture == | ||

| − | The PEZY-SC microprocessors is made of 4 blocks called "Prefectures". The Prefecture contains 2 | + | {{further|pezy/pezy-scx#Architecture|l1=PEZY-SCx § Architecture}} |

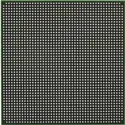

| + | The PEZY-SC microprocessors is made of 4 blocks called "Prefectures". The Prefecture contains 2 MiB of L3$ enclosed by 16 smaller blocks called "Cities". Each City is made of 64 KiB of L2$, a number of special function units, and 4 smaller blocks called "Villages". A village is a block of 4 execution units. For every 2 execution units there is 2 KiB of L1D$. | ||

[[File:pezy-sc arch.svg|700px]] | [[File:pezy-sc arch.svg|700px]] | ||

| − | |||

| − | |||

| − | |||

| − | |||

== Cache == | == Cache == | ||

PEZY-SC's cache is separate from the {{armh|ARM926}}'s cache which has an L1$ of 32 KiB (2x) and 64 KiB L2$ (shared). | PEZY-SC's cache is separate from the {{armh|ARM926}}'s cache which has an L1$ of 32 KiB (2x) and 64 KiB L2$ (shared). | ||

| + | {{cache size | ||

| + | |l1 cache=64 KiB | ||

| + | |l1i cache=32 KiB | ||

| + | |l1i break=2x16 KiB | ||

| + | |l1d cache=32 KiB | ||

| + | |l1d break=2x16 KiB | ||

| + | |l2 cache=64 KiB | ||

| + | |l2 break=1x64 KiB | ||

| + | }} | ||

| + | |||

| + | The chip integrates a multi-level cache hierarchy: | ||

{{cache size | {{cache size | ||

|l1 cache=3 MiB | |l1 cache=3 MiB | ||

| Line 68: | Line 74: | ||

|l3 policy= | |l3 policy= | ||

}} | }} | ||

| + | |||

| + | Additionally, there is another 16 MiB of scratch-pad memory consisting of 16 KiB per PE. | ||

== Memory controller == | == Memory controller == | ||

| Line 85: | Line 93: | ||

== Expansions == | == Expansions == | ||

| − | {{expansions | + | {{expansions main |

| − | | | + | | |

| − | | | + | {{expansions entry |

| − | | pcie | + | |type=PCIe |

| − | | pcie | + | |pcie revision=2.0 |

| − | | pcie config | + | |pcie lanes=32 |

| − | + | |pcie config=4x8 | |

| − | + | }} | |

}} | }} | ||

| Line 99: | Line 107: | ||

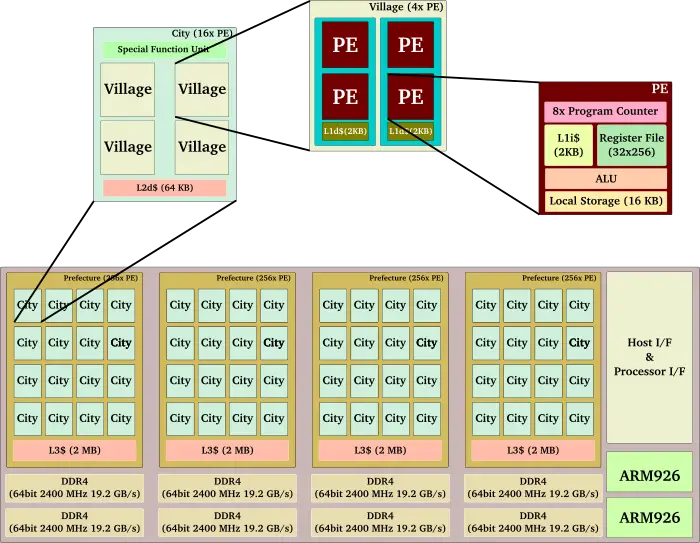

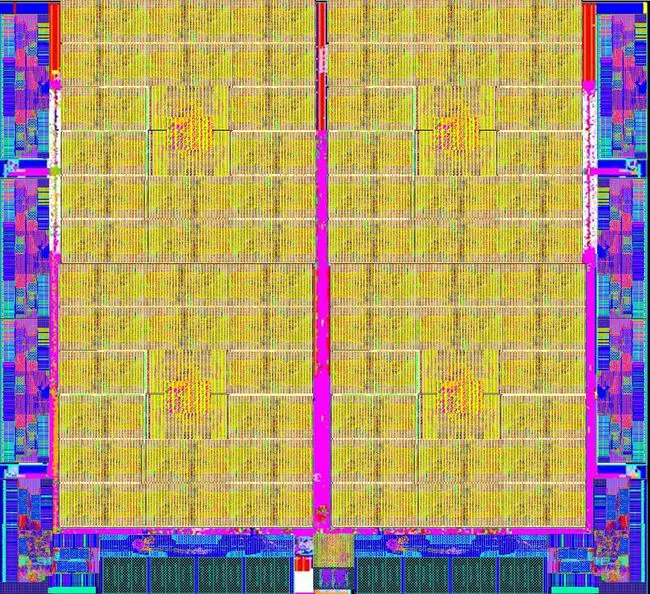

* 19.5 mm × 21.1 mm | * 19.5 mm × 21.1 mm | ||

* 411.6 mm² die size | * 411.6 mm² die size | ||

| − | |||

| + | :[[File:pezy sc die shot.jpg|650px]] | ||

| + | |||

| + | |||

| + | :[[File:pezy-sc die shot (annotated).png|650px]] | ||

| + | |||

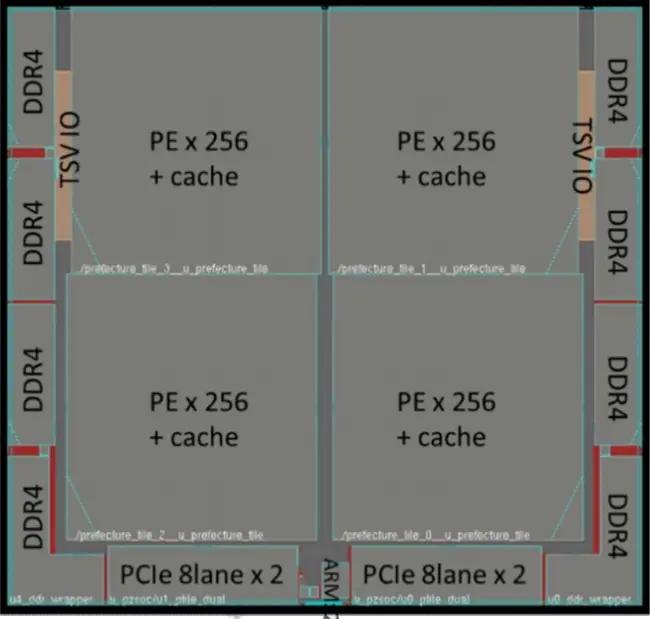

| + | === Floorplan === | ||

| − | [[File:pezy-sc | + | :[[File:pezy-sc floorplan.png|650px]] |

== External Links == | == External Links == | ||

Latest revision as of 11:14, 22 September 2018

| Edit Values | ||||||||||

| PEZY-SC | ||||||||||

| ||||||||||

| General Info | ||||||||||

| Designer | PEZY | |||||||||

| Manufacturer | TSMC | |||||||||

| Model Number | PEZY-SC | |||||||||

| Market | Supercomputer | |||||||||

| Introduction | 2013 (announced) September, 2014 (launched) | |||||||||

| General Specs | ||||||||||

| Family | PEZY-SCx | |||||||||

| Frequency | 733.33 MHz | |||||||||

| Microarchitecture | ||||||||||

| Process | 28 nm | |||||||||

| Transistors | 3,730,000,000 | |||||||||

| Technology | CMOS | |||||||||

| Die | 411.6 mm² 19.5 mm × 21.1 mm | |||||||||

| Cores | 1,024 | |||||||||

| Threads | 8,192 | |||||||||

| Electrical | ||||||||||

| Power dissipation | 100 W | |||||||||

| Power dissipation (average) | 70 W | |||||||||

| Vcore | 1.0 V | |||||||||

| Packaging | ||||||||||

| ||||||||||

PEZY-SC (PEZY Super Computer) is a second generation many-core microprocessor developed by PEZY and introduced in 2014. This chip, which operates at 733 MHz, incorporates 1,024 cores dissipating 100 W. The PEZY-SC powers the ZettaScaler-1.x series of supercomputers. The PEZY-SC is used in a number of TOP500 & Green500 supercomputers as the world's most efficient supercomputers.

Contents

Overview[edit]

- See also: PEZY-1

The PEZY-SC (SC for "Super Computer") is PEZY's second generation microprocessors which builds upon the PEZY-1. The chip contains exactly twice as many cores and incorporates a large amount of cache including 8 MB of L3$. The chip contains 2 ARM926 cores (ARMv5TEJ) along with 1,024 simpler cores supporting 8-way SMT for a total of 8,192 threads. Operating at 733 MHz, the processor has a peak performance of 3.0 TFLOPS (single-precision) and 1.5 TFLOPS (double-precision). PEZY-SC was designed using 580 million gates and manufactured on TSMC's 28HPC+.

The chip has a peak power dissipation of 100 W with a typical power consumption of 70 W which consists of 10 W leakage + 60 W dynamic.

In June of 2015, PEZY-SC-based supercomputers took all top 3 spots on the Green500 listing as the 3 most efficient supercomputers. PEZY-SC powers Shoubu (1,181,952 cores, ? kW, 605.624 TFlop/s Linpack Rmax), and Suiren Blue (262,656 cores, 40.86 kW, 247.752 TFlop/s Linpack Rmax), and Suiren (328,480 cores, 48.90 kW, 271.782 TFlop/s Linpack Rmax) supercomputers (ranked 1, 2, and 3 respectively).

Architecture[edit]

- Further information: PEZY-SCx § Architecture

The PEZY-SC microprocessors is made of 4 blocks called "Prefectures". The Prefecture contains 2 MiB of L3$ enclosed by 16 smaller blocks called "Cities". Each City is made of 64 KiB of L2$, a number of special function units, and 4 smaller blocks called "Villages". A village is a block of 4 execution units. For every 2 execution units there is 2 KiB of L1D$.

Cache[edit]

PEZY-SC's cache is separate from the ARM926's cache which has an L1$ of 32 KiB (2x) and 64 KiB L2$ (shared).

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

The chip integrates a multi-level cache hierarchy:

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Additionally, there is another 16 MiB of scratch-pad memory consisting of 16 KiB per PE.

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions[edit]

Expansion Options |

|||||

|

|||||

Die Shot[edit]

- 28 nm process

- 19.5 mm × 21.1 mm

- 411.6 mm² die size

Floorplan[edit]

External Links[edit]

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | PEZY-SC - PEZY#io + |

| has ecc memory support | true + |

| l1$ size | 3,072 KiB (3,145,728 B, 3 MiB) + |

| l1d$ description | per 2 processor elements + |

| l1d$ size | 1,024 KiB (1,048,576 B, 1 MiB) + |

| l1i$ description | per processor element + |

| l1i$ size | 2,048 KiB (2,097,152 B, 2 MiB) + |

| l2$ description | per city + |

| l2$ size | 4 MiB (4,096 KiB, 4,194,304 B, 0.00391 GiB) + |

| l3$ description | per prefecture + |

| l3$ size | 8 MiB (8,192 KiB, 8,388,608 B, 0.00781 GiB) + |

| max memory bandwidth | 127.156 GiB/s (130,207.744 MiB/s, 136.533 GB/s, 136,532.715 MB/s, 0.124 TiB/s, 0.137 TB/s) + |

| max memory channels | 8 + |

| max pcie lanes | 24 + |

| supported memory type | DDR4-2133 + |