From WikiChip

Difference between revisions of "WikiChip:sandbox"

(→comptable) |

|||

| (7 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

| + | <div id="wc_menu_export"></div>@@_START_A_BUTTON_@@<i class="fa fa-company-intel" aria-hidden="true"></i><span class="mob-collapse"> Intel <i class="fa fa-angle-down" aria-hidden="true"></i></span>@@_END_A_BUTTON_@@<div style="padding: 20px;" class="collapse"> | ||

| + | <div><span style="font-size: 1.2em; margin: 10px; display: block;">Popular Families</span><hr style="display: block; height: 1px; border: 0; border-top: 1px solid #b7b7b7; margin: 1em 0; padding: 0;"><div style="display: flex;"><ul class="items"><li>@@_START_H5_@@Intel@@_END_H5_@@<ul style="list-style:none; display: flex; flex-direction: column;"><li>Core i3</li></ul></li></ul></div></div> | ||

| + | <div><span style="font-size: 1.2em; margin: 10px; display: block;">Popular Families</span><hr style="display: block; height: 1px; border: 0; border-top: 1px solid #b7b7b7; margin: 1em 0; padding: 0;"><div style="display: flex;"><ul class="items"><li>@@_START_H5_@@Intel@@_END_H5_@@<ul style="list-style:none; display: flex; flex-direction: column;"><li>Core i3</li></ul></li></ul></div></div> | ||

| + | <div><span style="font-size: 1.2em; margin: 10px; display: block;">Popular Families</span><hr style="display: block; height: 1px; border: 0; border-top: 1px solid #b7b7b7; margin: 1em 0; padding: 0;"><div style="display: flex;"><ul class="items"><li>@@_START_H5_@@Intel@@_END_H5_@@<ul style="list-style:none; display: flex; flex-direction: column;"><li>Core i3</li></ul></li></ul></div></div> | ||

| + | </div><div id="wc_menu_export"></div> | ||

Welcome to this sandbox page. Sandbox pages provide space to experiment with the process of editing. | Welcome to this sandbox page. Sandbox pages provide space to experiment with the process of editing. | ||

<hr /> | <hr /> | ||

| + | === <span style="float: right;">header text right</span> === | ||

| + | == test == | ||

<table style="border: 1px solid black; border-collapse: collapse; border-spacing:0; text-align: center;"> | <table style="border: 1px solid black; border-collapse: collapse; border-spacing:0; text-align: center;"> | ||

<tr><td colspan="9">ssssssssssss</td></tr> | <tr><td colspan="9">ssssssssssss</td></tr> | ||

| Line 89: | Line 96: | ||

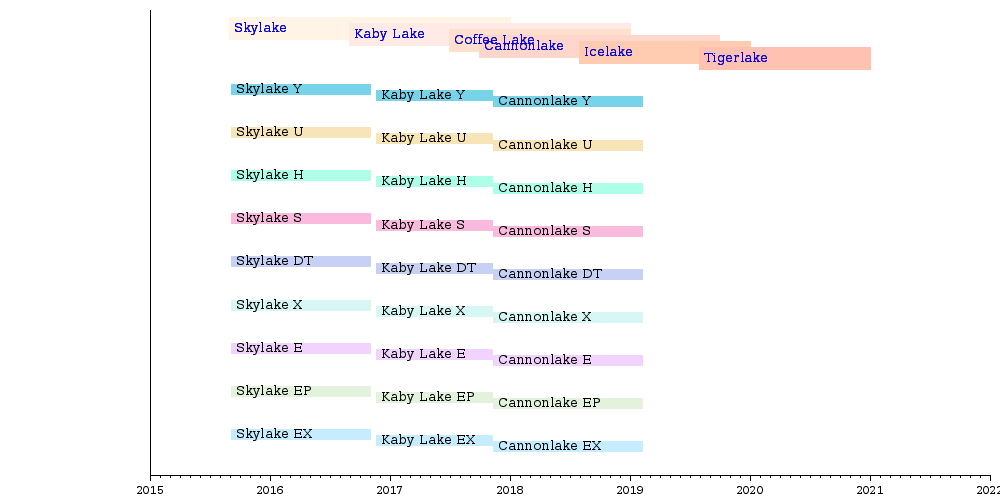

== comptable == | == comptable == | ||

| + | {{#invoke: arch timeline|intel_x86}} | ||

| + | |||

| + | {{#time:09/01/2015}} | ||

| + | |||

<timeline> | <timeline> | ||

| − | ImageSize = width:1000 height: | + | ImageSize = width:1000 height:500 |

| − | PlotArea = left: | + | PlotArea = left:150 right:10 top:10 bottom:25 #left:0 right:0 bottom:20 top:0 |

DateFormat = mm/dd/yyyy | DateFormat = mm/dd/yyyy | ||

| Line 114: | Line 125: | ||

id:c_core1 value:rgb(0.47,0.83,0.91) | id:c_core1 value:rgb(0.47,0.83,0.91) | ||

id:c_core2 value:rgb(0.97,0.90,0.72) | id:c_core2 value:rgb(0.97,0.90,0.72) | ||

| − | id:c_core3 value:rgb(0. | + | id:c_core3 value:rgb(0.68,1,0.91) |

| − | id:c_core4 value:rgb(0. | + | id:c_core4 value:rgb(0.98,0.73,0.87) |

| − | id:c_core5 value:rgb(0. | + | id:c_core5 value:rgb(0.78,0.82,0.96) |

| − | id:c_core6 value:rgb(0. | + | id:c_core6 value:rgb(0.84,0.97,0.96) |

| − | id:c_core7 value:rgb(0. | + | id:c_core7 value:rgb(0.95,0.83,1) |

| − | id:c_core8 value:rgb(0. | + | id:c_core8 value:rgb(0.89,0.95,0.87) |

id:c_core9 value:rgb(0.78,0.93,1) | id:c_core9 value:rgb(0.78,0.93,1) | ||

| Line 133: | Line 144: | ||

bar:arch8 | bar:arch8 | ||

bar:arch9 | bar:arch9 | ||

| − | barset: | + | barset:Cores1 |

| − | bar: | + | bar:core11 |

| − | bar: | + | bar:core12 |

| − | bar: | + | bar:core13 |

| − | bar: | + | bar:core14 |

| − | bar: | + | bar:core15 |

| − | bar: | + | bar:core16 |

| − | bar: | + | barset:Cores2 |

| − | bar: | + | bar:core21 |

| − | bar: | + | bar:core22 |

| + | bar:core23 | ||

| + | bar:core24 | ||

| + | bar:core25 | ||

| + | bar:core26 | ||

| + | barset:Cores3 | ||

| + | bar:core31 | ||

| + | bar:core32 | ||

| + | bar:core33 | ||

| + | bar:core34 | ||

| + | bar:core35 | ||

| + | bar:core36 | ||

| + | barset:Cores4 | ||

| + | bar:core41 | ||

| + | bar:core42 | ||

| + | bar:core43 | ||

| + | bar:core44 | ||

| + | bar:core45 | ||

| + | bar:core46 | ||

| + | barset:Cores5 | ||

| + | bar:core51 | ||

| + | bar:core52 | ||

| + | bar:core53 | ||

| + | bar:core54 | ||

| + | bar:core55 | ||

| + | bar:core56 | ||

| + | barset:Cores6 | ||

| + | bar:core61 | ||

| + | bar:core62 | ||

| + | bar:core63 | ||

| + | bar:core64 | ||

| + | bar:core65 | ||

| + | bar:core66 | ||

| + | barset:Cores7 | ||

| + | bar:core71 | ||

| + | bar:core72 | ||

| + | bar:core73 | ||

| + | bar:core74 | ||

| + | bar:core75 | ||

| + | bar:core76 | ||

| + | barset:Cores8 | ||

| + | bar:core81 | ||

| + | bar:core82 | ||

| + | bar:core83 | ||

| + | bar:core84 | ||

| + | bar:core85 | ||

| + | bar:core86 | ||

| + | barset:Cores9 | ||

| + | bar:core91 | ||

| + | bar:core92 | ||

| + | bar:core93 | ||

| + | bar:core94 | ||

| + | bar:core95 | ||

| + | bar:core96 | ||

PlotData= | PlotData= | ||

width:22 fontsize:10 textcolor:black shift:(5,-4) | width:22 fontsize:10 textcolor:black shift:(5,-4) | ||

| Line 152: | Line 216: | ||

bar:arch6 color:c_arch6 from:08/01/2019 till:01/01/2021 anchor:from text:"[[intel/microarchitectures/tigerlake|Tigerlake]]" | bar:arch6 color:c_arch6 from:08/01/2019 till:01/01/2021 anchor:from text:"[[intel/microarchitectures/tigerlake|Tigerlake]]" | ||

| − | width: | + | width:10 fontsize:10 |

color:c_core1 | color:c_core1 | ||

| − | bar: | + | bar:core11 anchor:from from:09/05/2015 till:11/03/2016 text:"Skylake Y" |

| − | + | bar:core12 anchor:from from:11/20/2016 till:11/09/2017 text:"Kaby Lake Y" | |

| − | + | bar:core13 anchor:from from:11/12/2017 till:02/09/2019 text:"Cannonlake Y" | |

| − | |||

color:c_core2 | color:c_core2 | ||

| − | bar: | + | bar:core21 anchor:from from:09/05/2015 till:11/03/2016 text:"Skylake U" |

| − | + | bar:core22 anchor:from from:11/20/2016 till:11/09/2017 text:"Kaby Lake U" | |

| − | + | bar:core23 anchor:from from:11/12/2017 till:02/09/2019 text:"Cannonlake U" | |

color:c_core3 | color:c_core3 | ||

| − | bar: | + | bar:core31 anchor:from from:09/05/2015 till:11/03/2016 text:"Skylake H" |

| − | + | bar:core32 anchor:from from:11/20/2016 till:11/09/2017 text:"Kaby Lake H" | |

| − | + | bar:core33 anchor:from from:11/12/2017 till:02/09/2019 text:"Cannonlake H" | |

color:c_core4 | color:c_core4 | ||

| − | bar: | + | bar:core41 anchor:from from:09/05/2015 till:11/03/2016 text:"Skylake S" |

| − | + | bar:core42 anchor:from from:11/20/2016 till:11/09/2017 text:"Kaby Lake S" | |

| − | + | bar:core43 anchor:from from:11/12/2017 till:02/09/2019 text:"Cannonlake S" | |

color:c_core5 | color:c_core5 | ||

| − | bar: | + | bar:core51 anchor:from from:09/05/2015 till:11/03/2016 text:"Skylake DT" |

| − | + | bar:core52 anchor:from from:11/20/2016 till:11/09/2017 text:"Kaby Lake DT" | |

| − | + | bar:core53 anchor:from from:11/12/2017 till:02/09/2019 text:"Cannonlake DT" | |

color:c_core6 | color:c_core6 | ||

| − | bar: | + | bar:core61 anchor:from from:09/05/2015 till:11/03/2016 text:"Skylake X" |

| − | + | bar:core62 anchor:from from:11/20/2016 till:11/09/2017 text:"Kaby Lake X" | |

| − | + | bar:core63 anchor:from from:11/12/2017 till:02/09/2019 text:"Cannonlake X" | |

color:c_core7 | color:c_core7 | ||

| − | bar: | + | bar:core71 anchor:from from:09/05/2015 till:11/03/2016 text:"Skylake E" |

| − | + | bar:core72 anchor:from from:11/20/2016 till:11/09/2017 text:"Kaby Lake E" | |

| − | + | bar:core73 anchor:from from:11/12/2017 till:02/09/2019 text:"Cannonlake E" | |

color:c_core8 | color:c_core8 | ||

| − | bar: | + | bar:core81 anchor:from from:09/05/2015 till:11/03/2016 text:"Skylake EP" |

| − | + | bar:core82 anchor:from from:11/20/2016 till:11/09/2017 text:"Kaby Lake EP" | |

| − | + | bar:core83 anchor:from from:11/12/2017 till:02/09/2019 text:"Cannonlake EP" | |

color:c_core9 | color:c_core9 | ||

| − | bar: | + | bar:core91 anchor:from from:09/05/2015 till:11/03/2016 text:"Skylake EX" |

| − | + | bar:core92 anchor:from from:11/20/2016 till:11/09/2017 text:"Kaby Lake EX" | |

| − | + | bar:core93 anchor:from from:11/12/2017 till:02/09/2019 text:"Cannonlake EX" | |

</timeline> | </timeline> | ||

Latest revision as of 21:32, 7 February 2020

Welcome to this sandbox page. Sandbox pages provide space to experiment with the process of editing.

Contents

header text right[edit]

test[edit]

| ssssssssssss | ||||||||

| DATA BUS I/O | D0 | 01 | 16 | CM-RAM0 | X | |||

| D1 | 02 | 15 | CM-RAM1 | X | ||||

| D2 | 03 | 14 | CM-RAM2 | X | ||||

| D3 | 04 | 13 | CM-RAM3 | X | ||||

| Vss | 05 | 12 | Vdd | X | ||||

| CLOCK PHASE 1/2 | Ø1 | 06 | 11 | CM-ROM | X | |||

| Ø2 | 07 | 10 | TEST | X | ||||

| SYNC | 08 | 09 | RESET | X | ||||

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. [Edit Values]The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes. | ||||||||||||

| L1$ | 128 KiB |

| ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| L2$ | 128 KiB |

| ||||||||||

| L3$ | 128 KiB |

| ||||||||||

| L4$ | 128 KiB |

| ||||||||||

| Off-package cache support | ||||||||||||

| Mobo | 512 KiB |

| ||||||||||

wireless test[edit]

mpu[edit]

| AMD-X5-133ADW | |

| |

| General Info | |

| Designer | AMD |

|---|---|

| Manufacturer | AMD |

| Model Number | AMD-X5-133ADW |

| Part Number | AMD-X5-133ADW, AMD-X5-133ADW, AMD-X5-133ADW |

| Market | Desktop |

| Market | Desktop |

comptable[edit]

Script error: The function "intel_x86" does not exist.

09/01/2015

Tabl test[edit]

Microarchitecture template[edit]

| Microarchitectures | ||

| Paradigms | ||

| Single-Cycle | Multi-Cycle | Pipelining |

| Superpipelining | Superscalar | OOoE |

| Pipeline | ||

| Prefetching (instruction prefetch) | ||

| Fetching (instruction fetch) | ||

| Decoding (instruction decode) | ||

| micro-operation | macro-operation | internal operation |

| µOP cache | µOP fusion | |

| Out-of-Order | ||

| OOoE | Speculative | Flushing |

| Components | ||