From WikiChip

Difference between revisions of "loongson/godson 2/2g"

m (Bot: moving all {{mpu}} to {{chip}}) |

|||

| (13 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{loongson title|Godson-2G}} | {{loongson title|Godson-2G}} | ||

| − | {{ | + | {{chip |

| name = Godson-2G | | name = Godson-2G | ||

| image = godson-2g.jpg | | image = godson-2g.jpg | ||

| Line 9: | Line 9: | ||

| model number = 2G | | model number = 2G | ||

| part number = | | part number = | ||

| − | | part number | + | | part number 2 = |

| market = Desktop | | market = Desktop | ||

| first announced = April, 2009 | | first announced = April, 2009 | ||

| Line 19: | Line 19: | ||

| family = Godson 2 | | family = Godson 2 | ||

| series = Godson 2 | | series = Godson 2 | ||

| − | | locked = | + | | locked = |

| frequency = 1,000 MHz | | frequency = 1,000 MHz | ||

| frequency 2 = | | frequency 2 = | ||

| frequency N = | | frequency N = | ||

| − | | bus type = | + | | bus type = HyperTransport 1.0 |

| − | | bus speed = | + | | bus speed = 400 MHz |

| − | | bus rate = | + | | bus rate = |

| − | | bus links = | + | | bus links = |

| − | | clock multiplier = | + | | clock multiplier = 2.5 |

| isa family = MIPS | | isa family = MIPS | ||

| Line 39: | Line 39: | ||

| core stepping = | | core stepping = | ||

| process = 65 nm | | process = 65 nm | ||

| − | | transistors = | + | | transistors = 100,000,000 |

| technology = CMOS | | technology = CMOS | ||

| die area = 53.54 mm² | | die area = 53.54 mm² | ||

| Line 50: | Line 50: | ||

| max memory = | | max memory = | ||

| − | + | ||

| − | | power = | + | | power = 3 W |

| v core = | | v core = | ||

| v core tolerance = <!-- OR ... --> | | v core tolerance = <!-- OR ... --> | ||

| Line 79: | Line 79: | ||

| packaging = Yes | | packaging = Yes | ||

| − | | package 0 = FCBGA- | + | | package 0 = FCBGA-741 |

| package 0 type = FCBGA | | package 0 type = FCBGA | ||

| − | | package 0 pins = | + | | package 0 pins = 741 |

| package 0 pitch = | | package 0 pitch = | ||

| − | | package 0 width = | + | | package 0 width = 31 mm |

| − | | package 0 length = | + | | package 0 length = 31 mm |

| package 0 height = | | package 0 height = | ||

| − | | socket 0 = BGA- | + | | socket 0 = BGA-741 |

| socket 0 type = BGA | | socket 0 type = BGA | ||

}} | }} | ||

| − | '''Godson-2G''' is a {{arch|64}} [[MIPS]] performance processor developed by [[Institute of Computing Technology of the Chinese Academy of Sciences|ICT]] and later [[Loongson]] for desktop computers. Introduced in late-[[2010]], the Godson-2G operates at up to 1 GHz consuming up to | + | '''Godson-2G''' ('''龙芯2G''') is a {{arch|64}} [[MIPS]] performance processor developed by [[Institute of Computing Technology of the Chinese Academy of Sciences|ICT]] and later [[Loongson]] for desktop computers. Introduced in late-[[2010]], the Godson-2G operates at up to 1 GHz consuming up to 3 W. This chip was manufactured on [[STMicroelectronics]]' [[65 nm process]]. |

| + | |||

| + | This specific models incorporates a considerably larger [[2nd level cache]] compared to the rest of the {{\\\|Godson 2}} family along with an extended number of additional interfaces in a relatively large package. The Godson-2G integrates the majority of the [[southbridge]] on-die. | ||

| + | |||

| + | == Cache == | ||

| + | {{main|loongson/microarchitectures/GS464#Memory_Hierarchy|l1=GS464 § Cache}} | ||

| + | {{cache size | ||

| + | |l1 cache=128 KiB | ||

| + | |l1i cache=64 KiB | ||

| + | |l1i break=1x64 KiB | ||

| + | |l1i desc=4-way set associative | ||

| + | |l1d cache=64 KiB | ||

| + | |l1d break=1x64 KiB | ||

| + | |l1d desc=4-way set associative | ||

| + | |l1d policy= | ||

| + | |l2 cache=1 MiB | ||

| + | |l2 break=1x1 MiB | ||

| + | |l2 desc=4-way set associative | ||

| + | |l2 policy= | ||

| + | }} | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=DDR3-800 | ||

| + | |ecc=Yes | ||

| + | |max mem=4 GiB | ||

| + | |controllers=1 | ||

| + | |channels=1 | ||

| + | |max bandwidth=11.92 GiB/s | ||

| + | |bandwidth schan=11.92 GiB/s | ||

| + | }} | ||

| + | |||

| + | == Expansions == | ||

| + | This chip has integrated [[HyperTransport]] 1.0 operating at 400 MHz. | ||

| + | {{expansions | ||

| + | |pci width = 32 bit | ||

| + | |pci clock = 66 MHz | ||

| + | |pcix width = 32 bit | ||

| + | |pcix clock = 133 MHz | ||

| + | |lpc revision=1.1 | ||

| + | }} | ||

| + | |||

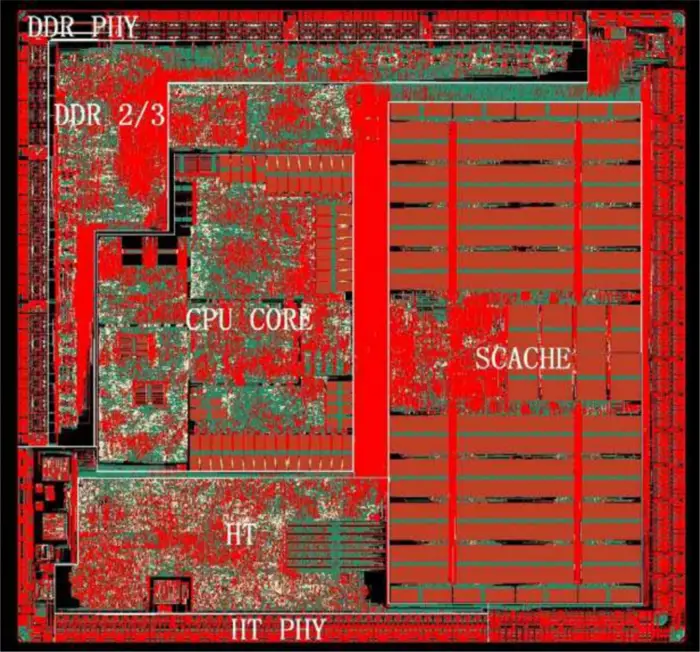

| + | == Die Shot == | ||

| + | * [[65 nm process]] | ||

| + | * 100,000,000 transistors | ||

| + | * 53.54 mm² die size | ||

| + | [[File:godson-2g die shot.png|700px]] | ||

== References == | == References == | ||

* Zhao, Ji-Ye, et al. "Physical Design Methodology for Godson-2G Microprocessor." Journal of Computer Science and Technology 25.2 (2010): 225-231. | * Zhao, Ji-Ye, et al. "Physical Design Methodology for Godson-2G Microprocessor." Journal of Computer Science and Technology 25.2 (2010): 225-231. | ||

| + | * Weiwu Hu, Yunji Chen. "GS464V: A High-Performance Low-Power XPU with 512-Bit Vector Extension". HotChips 22 (2010). | ||

| + | * Loongson Technology, "龙芯芯片产品技术白皮书" ("Godson chip product technology white paper") | ||

Latest revision as of 16:31, 13 December 2017

| Edit Values | |

| Godson-2G | |

| |

| Godson-2G chip | |

| General Info | |

| Designer | Loongson |

| Manufacturer | STMicroelectronics |

| Model Number | 2G |

| Market | Desktop |

| Introduction | April, 2009 (announced) November, 2010 (launched) |

| General Specs | |

| Family | Godson 2 |

| Series | Godson 2 |

| Frequency | 1,000 MHz |

| Bus type | HyperTransport 1.0 |

| Bus speed | 400 MHz |

| Clock multiplier | 2.5 |

| Microarchitecture | |

| ISA | MIPS64 (MIPS) |

| Microarchitecture | GS464 |

| Core Name | GS464 |

| Process | 65 nm |

| Transistors | 100,000,000 |

| Technology | CMOS |

| Die | 53.54 mm² |

| Word Size | 64 bit |

| Cores | 1 |

| Threads | 1 |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| Power dissipation | 3 W |

Godson-2G (龙芯2G) is a 64-bit MIPS performance processor developed by ICT and later Loongson for desktop computers. Introduced in late-2010, the Godson-2G operates at up to 1 GHz consuming up to 3 W. This chip was manufactured on STMicroelectronics' 65 nm process.

This specific models incorporates a considerably larger 2nd level cache compared to the rest of the Godson 2 family along with an extended number of additional interfaces in a relatively large package. The Godson-2G integrates the majority of the southbridge on-die.

Cache[edit]

- Main article: GS464 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions[edit]

This chip has integrated HyperTransport 1.0 operating at 400 MHz.

Die Shot[edit]

- 65 nm process

- 100,000,000 transistors

- 53.54 mm² die size

References[edit]

- Zhao, Ji-Ye, et al. "Physical Design Methodology for Godson-2G Microprocessor." Journal of Computer Science and Technology 25.2 (2010): 225-231.

- Weiwu Hu, Yunji Chen. "GS464V: A High-Performance Low-Power XPU with 512-Bit Vector Extension". HotChips 22 (2010).

- Loongson Technology, "龙芯芯片产品技术白皮书" ("Godson chip product technology white paper")

Facts about "Godson-2G - Loongson"

| base frequency | 1,000 MHz (1 GHz, 1,000,000 kHz) + |

| bus speed | 400 MHz (0.4 GHz, 400,000 kHz) + |

| bus type | HyperTransport 1.0 + |

| clock multiplier | 2.5 + |

| core count | 1 + |

| core name | GS464 + |

| designer | Loongson + |

| die area | 53.54 mm² (0.083 in², 0.535 cm², 53,540,000 µm²) + |

| family | Godson 2 + |

| first announced | April 2009 + |

| first launched | November 2010 + |

| full page name | loongson/godson 2/2g + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| isa | MIPS64 + |

| isa family | MIPS + |

| l1$ size | 128 KiB (131,072 B, 0.125 MiB) + |

| l1d$ description | 4-way set associative + |

| l1d$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l2$ description | 4-way set associative + |

| l2$ size | 1 MiB (1,024 KiB, 1,048,576 B, 9.765625e-4 GiB) + |

| ldate | November 2010 + |

| main image |  + + |

| main image caption | Godson-2G chip + |

| manufacturer | STMicroelectronics + |

| market segment | Desktop + |

| max cpu count | 1 + |

| max memory bandwidth | 11.92 GiB/s (12,206.08 MiB/s, 12.799 GB/s, 12,799.003 MB/s, 0.0116 TiB/s, 0.0128 TB/s) + |

| max memory channels | 1 + |

| microarchitecture | GS464 + |

| model number | 2G + |

| name | Godson-2G + |

| power dissipation | 3 W (3,000 mW, 0.00402 hp, 0.003 kW) + |

| process | 65 nm (0.065 μm, 6.5e-5 mm) + |

| series | Godson 2 + |

| smp max ways | 1 + |

| supported memory type | DDR3-800 + |

| technology | CMOS + |

| thread count | 1 + |

| transistor count | 100,000,000 + |

| word size | 64 bit (8 octets, 16 nibbles) + |