From WikiChip

Difference between revisions of "intel/xeon e7/e7-8860"

m (Bot: moving all {{mpu}} to {{chip}}) |

|||

| (8 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{intel title|Xeon E7-8860}} | {{intel title|Xeon E7-8860}} | ||

| − | {{ | + | {{chip |

| name = Xeon E7-8860 | | name = Xeon E7-8860 | ||

| no image = Yes | | no image = Yes | ||

| Line 10: | Line 10: | ||

| model number = E7-8860 | | model number = E7-8860 | ||

| part number = AT80615005760AB | | part number = AT80615005760AB | ||

| − | |||

| part number 2 = | | part number 2 = | ||

| part number 3 = | | part number 3 = | ||

| + | | part number 4 = | ||

| market = Server | | market = Server | ||

| first announced = April 5, 2011 | | first announced = April 5, 2011 | ||

| Line 44: | Line 44: | ||

| cpuid = 206F2 | | cpuid = 206F2 | ||

| + | | isa family = x86 | ||

| + | | isa = x86-64 | ||

| microarch = Westmere | | microarch = Westmere | ||

| platform = Boxboro | | platform = Boxboro | ||

| Line 61: | Line 63: | ||

| max memory = 4 TiB | | max memory = 4 TiB | ||

| − | + | ||

| v core = 1.35 V | | v core = 1.35 V | ||

| v core tolerance = | | v core tolerance = | ||

| Line 79: | Line 81: | ||

| tstorage max = 85 °C | | tstorage max = 85 °C | ||

| − | + | | package module 1 = {{packages/intel/lga-1567}} | |

| − | |||

| − | |||

| − | |||

| − | | package | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

}} | }} | ||

| − | '''Xeon E7-8860''' is a {{arch|64}} deca-core [[x86]] data center microprocessor that supports up to 8 sockets. This first generation {{intel|Xeon E7}} processor, {{intel|Westmere|Westmere}}-based, operates at a base frequency of 2.26 GHz with {{intel|turbo boost technology| | + | '''Xeon E7-8860''' is a {{arch|64}} deca-core [[x86]] data center microprocessor that supports up to 8 sockets. This first generation {{intel|Xeon E7}} processor, {{intel|Westmere|Westmere}}-based, operates at a base frequency of 2.26 GHz with {{intel|turbo boost technology|turbo}} frequency of 2.66 GHz for 2 active cores. This chip has a TDP of 130 W, supporting up to 4 channels of DDR3 with support of up to 4 TB of memory. |

== Cache == | == Cache == | ||

{{main|intel/microarchitectures/westmere#Memory_Hierarchy|l1=Westmere § Cache}} | {{main|intel/microarchitectures/westmere#Memory_Hierarchy|l1=Westmere § Cache}} | ||

{{cache size | {{cache size | ||

| − | |l1 cache = 640 KiB | + | |l1 cache=640 KiB |

|l1i cache=320 KiB | |l1i cache=320 KiB | ||

|l1i break=10x32 KiB | |l1i break=10x32 KiB | ||

| Line 104: | Line 97: | ||

|l1d desc=8-way set associative | |l1d desc=8-way set associative | ||

|l1d policy=write-back | |l1d policy=write-back | ||

| − | |l2 cache=2. | + | |l2 cache=2.5 MiB |

|l2 break=10x256 KiB | |l2 break=10x256 KiB | ||

|l2 desc=8-way set associative | |l2 desc=8-way set associative | ||

| Line 155: | Line 148: | ||

|avx=No | |avx=No | ||

|avx2=No | |avx2=No | ||

| − | + | ||

|abm=No | |abm=No | ||

|tbm=No | |tbm=No | ||

| Line 197: | Line 190: | ||

|rvi=No | |rvi=No | ||

}} | }} | ||

| + | |||

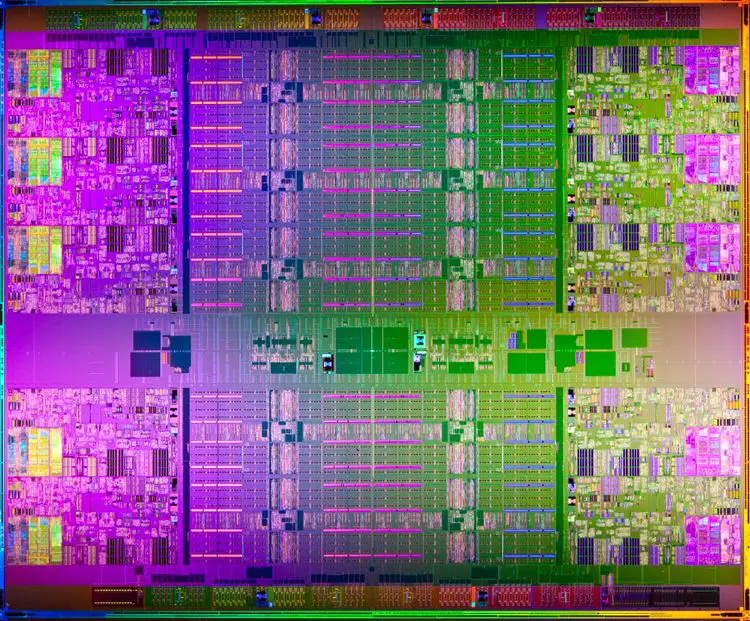

| + | == Die Shot == | ||

| + | [[File:intel xeon e7 die shot.jpg|750px]] | ||

| + | * 513 mm² | ||

| + | * 2,600,000,000 transistors | ||

| + | * 10 cores | ||

Latest revision as of 15:28, 13 December 2017

| Edit Values | ||||||||||||

| Xeon E7-8860 | ||||||||||||

| General Info | ||||||||||||

| Designer | Intel | |||||||||||

| Manufacturer | Intel | |||||||||||

| Model Number | E7-8860 | |||||||||||

| Part Number | AT80615005760AB | |||||||||||

| S-Spec | SLC3F | |||||||||||

| Market | Server | |||||||||||

| Introduction | April 5, 2011 (announced) April 5, 2011 (launched) | |||||||||||

| End-of-life | August 21, 2015 (last order) February 2, 2018 (last shipment) | |||||||||||

| Release Price | $4061.00 | |||||||||||

| Shop | Amazon | |||||||||||

| General Specs | ||||||||||||

| Family | Xeon E7 | |||||||||||

| Series | E7-8800 | |||||||||||

| Locked | Yes | |||||||||||

| Frequency | 2,266.66 MHz | |||||||||||

| Turbo Frequency | Yes | |||||||||||

| Turbo Frequency | 2,666.66 MHz (1 core), 2,666.66 MHz (2 cores), 2,666.66 MHz (3 cores), 2,666.66 MHz (4 cores), 2,533.33 MHz (5 cores), 2,533.33 MHz (6 cores), 2,399.99 MHz (7 cores), 2,399.99 MHz (8 cores), 2,399.99 MHz (9 cores), 2,399.99 MHz (10 cores) | |||||||||||

| Bus type | QPI | |||||||||||

| Bus rate | 6.40 GT/s | |||||||||||

| Clock multiplier | 17 | |||||||||||

| CPUID | 206F2 | |||||||||||

| Microarchitecture | ||||||||||||

| ISA | x86-64 (x86) | |||||||||||

| Microarchitecture | Westmere | |||||||||||

| Platform | Boxboro | |||||||||||

| Chipset | Boxboro | |||||||||||

| Core Name | Westmere EX | |||||||||||

| Core Family | 6 | |||||||||||

| Core Model | 47 | |||||||||||

| Core Stepping | A2 | |||||||||||

| Process | 32 nm | |||||||||||

| Transistors | 2,600,000,000 | |||||||||||

| Technology | CMOS | |||||||||||

| Die | 513 mm² | |||||||||||

| Word Size | 64 bit | |||||||||||

| Cores | 10 | |||||||||||

| Threads | 20 | |||||||||||

| Max Memory | 4 TiB | |||||||||||

| Multiprocessing | ||||||||||||

| Max SMP | 8-Way (Multiprocessor) | |||||||||||

| Electrical | ||||||||||||

| Vcore | 1.35 V | |||||||||||

| TDP | 130 W | |||||||||||

| Tcase | 5 °C – 69 °C | |||||||||||

| Tstorage | -40 °C – 85 °C | |||||||||||

| Packaging | ||||||||||||

| ||||||||||||

Xeon E7-8860 is a 64-bit deca-core x86 data center microprocessor that supports up to 8 sockets. This first generation Xeon E7 processor, Westmere-based, operates at a base frequency of 2.26 GHz with turbo frequency of 2.66 GHz for 2 active cores. This chip has a TDP of 130 W, supporting up to 4 channels of DDR3 with support of up to 4 TB of memory.

Cache[edit]

- Main article: Westmere § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Graphics[edit]

This SoC has no integrated graphics processing unit.

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Features[edit]

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||

Die Shot[edit]

- 513 mm²

- 2,600,000,000 transistors

- 10 cores

Facts about "Xeon E7-8860 - Intel"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Xeon E7-8860 - Intel#package + |

| base frequency | 2,266.66 MHz (2.267 GHz, 2,266,660 kHz) + |

| bus rate | 6,400 MT/s (6.4 GT/s, 6,400,000 kT/s) + |

| bus type | QPI + |

| chipset | Boxboro + |

| clock multiplier | 17 + |

| core count | 10 + |

| core family | 6 + |

| core model | 47 + |

| core name | Westmere EX + |

| core stepping | A2 + |

| core voltage | 1.35 V (13.5 dV, 135 cV, 1,350 mV) + |

| cpuid | 206F2 + |

| designer | Intel + |

| die area | 513 mm² (0.795 in², 5.13 cm², 513,000,000 µm²) + |

| family | Xeon E7 + |

| first announced | April 5, 2011 + |

| first launched | April 5, 2011 + |

| full page name | intel/xeon e7/e7-8860 + |

| has ecc memory support | true + |

| has extended page tables support | true + |

| has feature | Advanced Encryption Standard Instruction Set Extension +, Hyper-Threading Technology +, Turbo Boost Technology 1.0 +, Enhanced SpeedStep Technology +, Trusted Execution Technology +, Intel VT-x +, Intel VT-d + and Extended Page Tables + |

| has intel enhanced speedstep technology | true + |

| has intel trusted execution technology | true + |

| has intel turbo boost technology 1 0 | true + |

| has intel vt-d technology | true + |

| has intel vt-x technology | true + |

| has locked clock multiplier | true + |

| has second level address translation support | true + |

| has simultaneous multithreading | true + |

| has x86 advanced encryption standard instruction set extension | true + |

| instance of | microprocessor + |

| isa | x86-64 + |

| isa family | x86 + |

| l1$ size | 640 KiB (655,360 B, 0.625 MiB) + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 320 KiB (327,680 B, 0.313 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 320 KiB (327,680 B, 0.313 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 2.5 MiB (2,560 KiB, 2,621,440 B, 0.00244 GiB) + |

| l3$ description | 16-way set associative + |

| l3$ size | 24 MiB (24,576 KiB, 25,165,824 B, 0.0234 GiB) + |

| last order | August 21, 2015 + |

| last shipment | February 2, 2018 + |

| ldate | April 5, 2011 + |

| manufacturer | Intel + |

| market segment | Server + |

| max case temperature | 342.15 K (69 °C, 156.2 °F, 615.87 °R) + |

| max cpu count | 8 + |

| max memory | 4,194,304 MiB (4,294,967,296 KiB, 4,398,046,511,104 B, 4,096 GiB, 4 TiB) + |

| max memory bandwidth | 31.77 GiB/s (32,532.48 MiB/s, 34.113 GB/s, 34,112.778 MB/s, 0.031 TiB/s, 0.0341 TB/s) + |

| max memory channels | 4 + |

| max storage temperature | 358.15 K (85 °C, 185 °F, 644.67 °R) + |

| microarchitecture | Westmere + |

| min case temperature | 278.15 K (5 °C, 41 °F, 500.67 °R) + |

| min storage temperature | 233.15 K (-40 °C, -40 °F, 419.67 °R) + |

| model number | E7-8860 + |

| name | Xeon E7-8860 + |

| package | FCLGA-8 + |

| part number | AT80615005760AB + |

| platform | Boxboro + |

| process | 32 nm (0.032 μm, 3.2e-5 mm) + |

| release price | $ 4,061.00 (€ 3,654.90, £ 3,289.41, ¥ 419,623.13) + |

| s-spec | SLC3F + |

| series | E7-8800 + |

| smp max ways | 8 + |

| supported memory type | DDR3-1066 + |

| tdp | 130 W (130,000 mW, 0.174 hp, 0.13 kW) + |

| technology | CMOS + |

| thread count | 20 + |

| transistor count | 2,600,000,000 + |

| turbo frequency (10 cores) | 2,399.99 MHz (2.4 GHz, 2,399,990 kHz) + |

| turbo frequency (1 core) | 2,666.66 MHz (2.667 GHz, 2,666,660 kHz) + |

| turbo frequency (2 cores) | 2,666.66 MHz (2.667 GHz, 2,666,660 kHz) + |

| turbo frequency (3 cores) | 2,666.66 MHz (2.667 GHz, 2,666,660 kHz) + |

| turbo frequency (4 cores) | 2,666.66 MHz (2.667 GHz, 2,666,660 kHz) + |

| turbo frequency (5 cores) | 2,533.33 MHz (2.533 GHz, 2,533,330 kHz) + |

| turbo frequency (6 cores) | 2,533.33 MHz (2.533 GHz, 2,533,330 kHz) + |

| turbo frequency (7 cores) | 2,399.99 MHz (2.4 GHz, 2,399,990 kHz) + |

| turbo frequency (8 cores) | 2,399.99 MHz (2.4 GHz, 2,399,990 kHz) + |

| turbo frequency (9 cores) | 2,399.99 MHz (2.4 GHz, 2,399,990 kHz) + |

| word size | 64 bit (8 octets, 16 nibbles) + |