(a bit more detail) |

|||

| (7 intermediate revisions by 2 users not shown) | |||

| Line 19: | Line 19: | ||

| tech = CMOS | | tech = CMOS | ||

| clock min = 75 MHz | | clock min = 75 MHz | ||

| − | | clock max = | + | | clock max = 116.66 MHz |

| package = SPGA-296 | | package = SPGA-296 | ||

| package 2 = | | package 2 = | ||

| Line 34: | Line 34: | ||

== Overview == | == Overview == | ||

| − | K5 was a result of desperation and frustration with cloning and second-sourcing [[Intel]]-based [[x86]] microprocessors. Rumors for the development of K5 dates back to mid-[[1993]], however it was only officially announced in late [[1994]] with the goal of releasing the first batch of chips in in [[1995]]. K5, which stands for [[wikipedia:Kryptonite|Kryptonite]] 5, which as its name implied was an ambitious attempt by AMD to take on Intel (being [[wikipedia:Superman|Superman]], metaphorically). The design suffered significant delays first due to early design problems and later due to problems with various [[x86]] incompatibilities. The first few models were finally released in March of [[1996]]. | + | K5 was a result of desperation and frustration with cloning and second-sourcing [[Intel]]-based [[x86]] microprocessors. Rumors for the development of K5 dates back to mid-[[1993]], however it was only officially announced in late [[1994]] with the goal of releasing the first batch of chips in in [[1995]]. K5, which stands for [[wikipedia:Kryptonite|Kryptonite]] 5, which as its name implied was an ambitious attempt by AMD to take on Intel (being [[wikipedia:Superman|Superman]], metaphorically). The design suffered significant delays first due to early design problems and later due to problems with various [[x86]] incompatibilities. The first few models, using SSA/5, were finally released in March of [[1996]]. |

The first version of {{amd|microarchitectures/k5|K5 Microarchitecture}} introduced, '''SSA/5''', had many technical improvements over Intel's {{intel|Pentium}}, making it well ahead of its time. It had an instruction translator that converted [[CISC]] instructions into simpler [[RISC]] instructions. Due to numerous manufacturing issues and design choices, K5 failed to deliver the expected performance it should have. | The first version of {{amd|microarchitectures/k5|K5 Microarchitecture}} introduced, '''SSA/5''', had many technical improvements over Intel's {{intel|Pentium}}, making it well ahead of its time. It had an instruction translator that converted [[CISC]] instructions into simpler [[RISC]] instructions. Due to numerous manufacturing issues and design choices, K5 failed to deliver the expected performance it should have. | ||

AMD went back and readdressed some of the deficiencies the SSA/5 design had. AMD introduced the new version of K5, named '''5k86''', in October of 1996. AMD had reworked the way memory gets accessed and flows through, from [[L1$]] to [[L2$]] and main. The results is upward of 35% performance improvements across the board. 5k86's performance outmatched Pentium's with lower clock speed. | AMD went back and readdressed some of the deficiencies the SSA/5 design had. AMD introduced the new version of K5, named '''5k86''', in October of 1996. AMD had reworked the way memory gets accessed and flows through, from [[L1$]] to [[L2$]] and main. The results is upward of 35% performance improvements across the board. 5k86's performance outmatched Pentium's with lower clock speed. | ||

| + | |||

== Architecture == | == Architecture == | ||

{{main|amd/microarchitectures/k5|l1=K5 Microarchitecture}} | {{main|amd/microarchitectures/k5|l1=K5 Microarchitecture}} | ||

{{empty section}} | {{empty section}} | ||

| + | === Developers === | ||

| + | * Mike Johnson, Chief Architect | ||

| + | |||

| + | == Die Shot == | ||

| + | === {{\|AMD-K5-PR75ABR}} === | ||

| + | [[File:AMD K5 PR75 die.JPG|650px]] | ||

| + | |||

| + | === {{\|AMD-K5-PR150ABR}} === | ||

| + | [[File:AMD K5 die.JPG|650px]] | ||

== Members == | == Members == | ||

| − | {{ | + | AMD initially released SSA/5-based models, but they suffered great performance issues. AMD revised the microarchitecture, releasing 5k86-based models which out-performed Intel's Pentium clock for clock and were thus clocked at lower than the advertised Pentium Performance rating they were given. |

| + | |||

| + | === SSA/5-based models === | ||

| + | <!-- NOTE: | ||

| + | This table is generated automatically from the data in the actual articles. | ||

| + | If a microprocessor is missing from the list, an appropriate article for it needs to be | ||

| + | created and tagged accordingly. | ||

| + | |||

| + | Missing a chip? please dump its name here: http://en.wikichip.org/wiki/WikiChip:wanted_chips | ||

| + | --> | ||

| + | <table class="wikitable sortable"> | ||

| + | <tr><th colspan="11" style="background:#D6D6FF;">SSA/5-based Processors</th></tr> | ||

| + | <tr><th>Model</th><th>Launched</th><th>Process</th><th>Freq</th><th>Mult.</th><th>Bus</th><th>Max Mem</th><th>V<sub>CORE</sub></th><th>Package</th><th>Min T<sub>case</sub></th><th>Max T<sub>case</sub></th></tr> | ||

| + | {{#ask: [[Category:microprocessor models by amd]][[instance of::microprocessor]][[microprocessor family::K5]][[core name::SSA/5]] | ||

| + | |?full page name | ||

| + | |?model number | ||

| + | |?first launched | ||

| + | |?process | ||

| + | |?base frequency#MHz | ||

| + | |?clock multiplier | ||

| + | |?bus speed#MHz | ||

| + | |?max memory#GB | ||

| + | |?core voltage | ||

| + | |?package | ||

| + | |?min case temperature#°C | ||

| + | |?max case temperature#°C | ||

| + | |format=template | ||

| + | |template=proc table 2 | ||

| + | |userparam=12 | ||

| + | |sep=, | ||

| + | |mainlabel=- | ||

| + | }} | ||

| + | {{table count|col=11|ask=[[Category:microprocessor models by amd]][[instance of::microprocessor]][[microprocessor family::K5]][[core name::SSA/5]]}} | ||

| + | </table> | ||

| + | |||

| + | === 5k86-based models === | ||

| + | <!-- NOTE: | ||

| + | This table is generated automatically from the data in the actual articles. | ||

| + | If a microprocessor is missing from the list, an appropriate article for it needs to be | ||

| + | created and tagged accordingly. | ||

| + | |||

| + | Missing a chip? please dump its name here: http://en.wikichip.org/wiki/WikiChip:wanted_chips | ||

| + | --> | ||

| + | <table class="wikitable sortable"> | ||

| + | <tr><th colspan="11" style="background:#D6D6FF;">5k86-based Processors</th></tr> | ||

| + | <tr><th>Model</th><th>Launched</th><th>Process</th><th>Freq</th><th>Mult.</th><th>Bus</th><th>Max Mem</th><th>V<sub>CORE</sub></th><th>Package</th><th>Min T<sub>case</sub></th><th>Max T<sub>case</sub></th></tr> | ||

| + | {{#ask: [[Category:microprocessor models by amd]][[instance of::microprocessor]][[microprocessor family::K5]][[core name::5k86]] | ||

| + | |?full page name | ||

| + | |?model number | ||

| + | |?first launched | ||

| + | |?process | ||

| + | |?base frequency#MHz | ||

| + | |?clock multiplier | ||

| + | |?bus speed#MHz | ||

| + | |?max memory#GB | ||

| + | |?core voltage | ||

| + | |?package | ||

| + | |?min case temperature#°C | ||

| + | |?max case temperature#°C | ||

| + | |format=template | ||

| + | |template=proc table 2 | ||

| + | |userparam=12 | ||

| + | |sep=, | ||

| + | |mainlabel=- | ||

| + | }} | ||

| + | {{table count|col=11|ask=[[Category:microprocessor models by amd]][[instance of::microprocessor]][[microprocessor family::K5]][[core name::5k86]]}} | ||

| + | </table> | ||

| + | |||

| + | == Documents == | ||

| + | === DataSheet === | ||

| + | * [[:File:AMD-K5 Processor Data Sheet (January 1997).pdf|AMD K5 Processor Data Sheet]]; Publication #18522 Revision F/0; January 1997 | ||

| + | * [[:File:AMD-K5 Processor Technical Reference Manual (March 1996).pdf|AMD5<sub>k</sub>86 Processor Technical Reference Manual]]; Publication #18524 Revision B/0; March 1996 | ||

| + | * [[:File:AMD-K5 Processor Technical Reference Manual (November 1996).pdf|AMD-K5 Processor Technical Reference Manual]]; Publication #18524 Revision C/0; November 1996 | ||

| + | === Thermal & Clock === | ||

| + | * [[:File:Clock Gating Recommendations (Am486, Am5x86, K5) (August 1995).pdf|Clock Gating Recommendations]]; Publication #19195 Revision C/0; August 1995 | ||

| + | * [[:File:CPU Thermal Management (Am486, Am5x86, K5) (August 1995).pdf|CPU Thermal Management]]; Publication #18448 Revision D/0; August 1995. | ||

| + | * [[:File:Low Voltage Power Supply Circuits (Am486, Am5x86, K5) (August 1995).pdf|Low Voltage Power Supply Circuits]]; Publication #19197 Revision D/0; August 1995. | ||

| + | * [[:File:Phase Lock Loop (PLL) Clock Control (Am486, Am5x86, K5) (August 1995).pdf|Phase Lock Loop (PLL) Clock Control]]; Publication #18495 Revision D/0; August 1995. | ||

| + | === Other === | ||

| + | * [[:File:AMD-AMD-K5 PROCESSOR Software Development Guide (September 1996).pdf|AMD K5 PROCESSOR Software Development Guide]]; Publication #20007 Revision D/0; September 1996 | ||

| + | === PR === | ||

| + | * [[:File:AMD-K5 Processor Performance Brief (June, 1996).pdf|AMD-K5 Processor Performance Brief]]; Publication #20084 Revision B/0; June, 1996. | ||

| + | |||

| + | == See also == | ||

| + | * {{amd|K6}} | ||

| + | * {{intel|pentium (1992)|Pentium}} | ||

| + | * {{intel|Pentium Pro}} | ||

Latest revision as of 22:19, 17 June 2022

| AMD K5 | |

| |

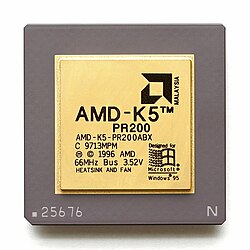

| K5-200 | |

| Developer | AMD |

| Manufacturer | AMD |

| Type | Microprocessors |

| Introduction | October 24, 1994 (announced) March 27, 1996 (launch) |

| Production | 1996 |

| Architecture | Pentium-compatible superscalar microprocessors |

| ISA | IA-32 |

| µarch | K5 |

| Word size | 32 bit 4 octets

8 nibbles |

| Process | 500 nm 0.5 μm , 350 nm5.0e-4 mm 0.35 μm

3.5e-4 mm |

| Technology | CMOS |

| Clock | 75 MHz-116.66 MHz |

| Package | SPGA-296 |

| Socket | Socket 5, Socket 7 |

| Succession | |

| ← | → |

| Am5x86 | K6 |

K5 was a family of microprocessors designed by AMD and introduced in 1996. K5 models directly rivaled Intel's Pentium processors. These processors were based on AMD's K5 Microarchitecture which was their first x86 microarchitecture to be designed in-house from the ground up without licensing or reverse-engineering Intel's architectures.

Contents

Overview[edit]

K5 was a result of desperation and frustration with cloning and second-sourcing Intel-based x86 microprocessors. Rumors for the development of K5 dates back to mid-1993, however it was only officially announced in late 1994 with the goal of releasing the first batch of chips in in 1995. K5, which stands for Kryptonite 5, which as its name implied was an ambitious attempt by AMD to take on Intel (being Superman, metaphorically). The design suffered significant delays first due to early design problems and later due to problems with various x86 incompatibilities. The first few models, using SSA/5, were finally released in March of 1996.

The first version of K5 Microarchitecture introduced, SSA/5, had many technical improvements over Intel's Pentium, making it well ahead of its time. It had an instruction translator that converted CISC instructions into simpler RISC instructions. Due to numerous manufacturing issues and design choices, K5 failed to deliver the expected performance it should have.

AMD went back and readdressed some of the deficiencies the SSA/5 design had. AMD introduced the new version of K5, named 5k86, in October of 1996. AMD had reworked the way memory gets accessed and flows through, from L1$ to L2$ and main. The results is upward of 35% performance improvements across the board. 5k86's performance outmatched Pentium's with lower clock speed.

Architecture[edit]

- Main article: K5 Microarchitecture

| This section is empty; you can help add the missing info by editing this page. |

Developers[edit]

- Mike Johnson, Chief Architect

Die Shot[edit]

AMD-K5-PR75ABR[edit]

AMD-K5-PR150ABR[edit]

Members[edit]

AMD initially released SSA/5-based models, but they suffered great performance issues. AMD revised the microarchitecture, releasing 5k86-based models which out-performed Intel's Pentium clock for clock and were thus clocked at lower than the advertised Pentium Performance rating they were given.

SSA/5-based models[edit]

,,,,,| SSA/5-based Processors | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Model | Launched | Process | Freq | Mult. | Bus | Max Mem | VCORE | Package | Min Tcase | Max Tcase |

| AMD-K5-PR100ABQ | 17 June 1996 | 350 nm 0.35 μm 3.5e-4 mm | 99.99 MHz 0.1 GHz 99,990 kHz | 1.5 | 66.66 MHz 0.0667 GHz 66,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 60 °C 333.15 K 140 °F 599.67 °R | |

| AMD-K5-PR100ABR | 17 June 1996 | 350 nm 0.35 μm 3.5e-4 mm | 99.99 MHz 0.1 GHz 99,990 kHz | 1.5 | 66.66 MHz 0.0667 GHz 66,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 70 °C 343.15 K 158 °F 617.67 °R | |

| AMD-K5-PR75ABR | 7 October 1996 | 350 nm 0.35 μm 3.5e-4 mm | 75 MHz 0.075 GHz 75,000 kHz | 1.5 | 50 MHz 0.05 GHz 50,000 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 70 °C 343.15 K 158 °F 617.67 °R | |

| AMD-K5-PR90ABQ | 7 October 1996 | 350 nm 0.35 μm 3.5e-4 mm | 90 MHz 0.09 GHz 90,000 kHz | 1.5 | 60 MHz 0.06 GHz 60,000 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 60 °C 333.15 K 140 °F 599.67 °R | |

| AMD-SSA/5-75ABR | 27 March 1996 | 500 nm 0.5 μm 5.0e-4 mm | 75 MHz 0.075 GHz 75,000 kHz | 1.5 | 50 MHz 0.05 GHz 50,000 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 70 °C 343.15 K 158 °F 617.67 °R | |

| AMD-SSA/5-90ABQ | 27 March 1996 | 500 nm 0.5 μm 5.0e-4 mm | 90 MHz 0.09 GHz 90,000 kHz | 1.5 | 60 MHz 0.06 GHz 60,000 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 60 °C 333.15 K 140 °F 599.67 °R | |

| Count: 6 | ||||||||||

5k86-based models[edit]

,,,,,,,,| 5k86-based Processors | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Model | Launched | Process | Freq | Mult. | Bus | Max Mem | VCORE | Package | Min Tcase | Max Tcase |

| AMD-K5-PR120ABQ | 7 October 1996 | 350 nm 0.35 μm 3.5e-4 mm | 90 MHz 0.09 GHz 90,000 kHz | 1.5 | 60 MHz 0.06 GHz 60,000 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 60 °C 333.15 K 140 °F 599.67 °R | |

| AMD-K5-PR120ABR | 7 October 1996 | 350 nm 0.35 μm 3.5e-4 mm | 90 MHz 0.09 GHz 90,000 kHz | 1.5 | 60 MHz 0.06 GHz 60,000 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 70 °C 343.15 K 158 °F 617.67 °R | |

| AMD-K5-PR133ABQ | 7 October 1996 | 350 nm 0.35 μm 3.5e-4 mm | 99.99 MHz 0.1 GHz 99,990 kHz | 1.5 | 66.66 MHz 0.0667 GHz 66,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 60 °C 333.15 K 140 °F 599.67 °R | |

| AMD-K5-PR133ABR | 7 October 1996 | 350 nm 0.35 μm 3.5e-4 mm | 99.99 MHz 0.1 GHz 99,990 kHz | 1.5 | 66.66 MHz 0.0667 GHz 66,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 70 °C 343.15 K 158 °F 617.67 °R | |

| AMD-K5-PR150ABR | 6 January 1997 | 350 nm 0.35 μm 3.5e-4 mm | 105 MHz 0.105 GHz 105,000 kHz | 1.75 | 60 MHz 0.06 GHz 60,000 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 70 °C 343.15 K 158 °F 617.67 °R | |

| AMD-K5-PR166ABQ | 6 January 1997 | 350 nm 0.35 μm 3.5e-4 mm | 116.66 MHz 0.117 GHz 116,660 kHz | 1.75 | 66.66 MHz 0.0667 GHz 66,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 60 °C 333.15 K 140 °F 599.67 °R | |

| AMD-K5-PR166ABR | 6 January 1997 | 350 nm 0.35 μm 3.5e-4 mm | 116.66 MHz 0.117 GHz 116,660 kHz | 1.75 | 66.66 MHz 0.0667 GHz 66,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 70 °C 343.15 K 158 °F 617.67 °R | |

| AMD-K5-PR166ABX | 6 January 1997 | 350 nm 0.35 μm 3.5e-4 mm | 116.66 MHz 0.117 GHz 116,660 kHz | 1.75 | 66.66 MHz 0.0667 GHz 66,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 65 °C 338.15 K 149 °F 608.67 °R | |

| AMD-K5-PR200ABX | April 1997 | 350 nm 0.35 μm 3.5e-4 mm | 133.33 MHz 0.133 GHz 133,330 kHz | 2 | 66.66 MHz 0.0667 GHz 66,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB | 3.525 V 35.25 dV 352.5 cV 3,525 mV | 0 °C 273.15 K 32 °F 491.67 °R | 65 °C 338.15 K 149 °F 608.67 °R | |

| Count: 9 | ||||||||||

Documents[edit]

DataSheet[edit]

- AMD K5 Processor Data Sheet; Publication #18522 Revision F/0; January 1997

- AMD5k86 Processor Technical Reference Manual; Publication #18524 Revision B/0; March 1996

- AMD-K5 Processor Technical Reference Manual; Publication #18524 Revision C/0; November 1996

Thermal & Clock[edit]

- Clock Gating Recommendations; Publication #19195 Revision C/0; August 1995

- CPU Thermal Management; Publication #18448 Revision D/0; August 1995.

- Low Voltage Power Supply Circuits; Publication #19197 Revision D/0; August 1995.

- Phase Lock Loop (PLL) Clock Control; Publication #18495 Revision D/0; August 1995.

Other[edit]

- AMD K5 PROCESSOR Software Development Guide; Publication #20007 Revision D/0; September 1996

PR[edit]

- AMD-K5 Processor Performance Brief; Publication #20084 Revision B/0; June, 1996.

See also[edit]

| designer | AMD + |

| first announced | October 24, 1994 + |

| first launched | March 27, 1996 + |

| full page name | amd/k5 + |

| instance of | microprocessor family + |

| instruction set architecture | IA-32 + |

| main designer | AMD + |

| manufacturer | AMD + |

| microarchitecture | K5 + |

| name | AMD K5 + |

| package | SPGA-296 + |

| process | 500 nm (0.5 μm, 5.0e-4 mm) + and 350 nm (0.35 μm, 3.5e-4 mm) + |

| socket | Socket 5 + and Socket 7 + |

| technology | CMOS + |

| word size | 32 bit (4 octets, 8 nibbles) + |