From WikiChip

Difference between revisions of "amd/microarchitectures/zen 4"

(→Key changes from {{\\|Zen 3}}: CES announcements) |

|||

| Line 48: | Line 48: | ||

=== Key changes from {{\\|Zen 3}} === | === Key changes from {{\\|Zen 3}} === | ||

{{empty section}} | {{empty section}} | ||

| − | * | + | * Raised maximum core/thread count from 64/128 to at least 96/192 (vastly due to 5nm process allowing more space, therefore more cores). |

| − | * | + | * Improved cache load, write and prefetch from/to register (less latency). |

| − | * | + | * Utilizes new AM5 socket and is expected to support DDR5 and confirmed PCI-E 5. |

| − | + | * More transistors (depending on AM5 socket as well and not just the CPU it self). | |

| − | * | + | *Double the L2 cache when compared to Zen 3 |

| − | * | + | *Capable of higher all-core clockspeeds (shown 5GHz+) |

== Bibliography == | == Bibliography == | ||

Revision as of 19:43, 8 January 2022

| Edit Values | |

| Zen 4 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | AMD |

| Manufacturer | TSMC |

| Process | 5 nm |

| Succession | |

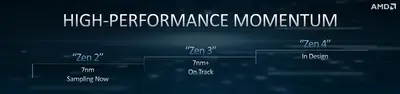

Zen 4 is a planned microarchitecture being developed by AMD as a successor to Zen 3.

Contents

History

Zen 4 was first mentioned by Forrest Norrod during AMD's EPYC One Year Anniversary webinar. During the next horizon event which was held on November 6, 2018, AMD stated that Zen 4 was at the design completion phase.

Process Technology

AMD claims that Zen4 is going to be produced on a 5nm node by TSMC.

Codenames

| Core | C/T | Target |

|---|---|---|

| Genoa | Up to 96/192 | High-end server multiprocessors |

| Warhol | Up to 20/40 | Mainstream to high-end desktops & enthusiasts market processors |

| Rembrandt | Up to 8/16 | Mainstream desktop & mobile processors with GPU |

Cores using variant Zen 4 uarch:

| Core | C/T | Target |

|---|---|---|

| Bergamo | Up to 128/128? | Cloud multiprocessing (smaller, almost half-size Zen 4c [referred to as “Zen 4D” in leaks] core likely sacrificing AVX-512, L3 and possibly SMT) |

Architecture

Little is currently known about the architectural improvements that are being done to Zen 4.

Key changes from Zen 3

| This section is empty; you can help add the missing info by editing this page. |

- Raised maximum core/thread count from 64/128 to at least 96/192 (vastly due to 5nm process allowing more space, therefore more cores).

- Improved cache load, write and prefetch from/to register (less latency).

- Utilizes new AM5 socket and is expected to support DDR5 and confirmed PCI-E 5.

- More transistors (depending on AM5 socket as well and not just the CPU it self).

- Double the L2 cache when compared to Zen 3

- Capable of higher all-core clockspeeds (shown 5GHz+)

Bibliography

Designers

- Mike Clark(?), chief architect

Bibliography

See Also

- AMD Zen

- Intel Meteor Lake

Facts about "Zen 4 - Microarchitectures - AMD"

| codename | Zen 4 + |

| designer | AMD + |

| full page name | amd/microarchitectures/zen 4 + |

| instance of | microarchitecture + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Zen 4 + |

| process | 5 nm (0.005 μm, 5.0e-6 mm) + |