(Cascade Lake R) |

(→Common Features) |

||

| (4 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

{{intel title|Cascade Lake R|core}} | {{intel title|Cascade Lake R|core}} | ||

{{core | {{core | ||

| − | |name=Cascade Lake | + | |name=Cascade Lake R |

|image=cascade lake sp (front).png | |image=cascade lake sp (front).png | ||

|developer=Intel | |developer=Intel | ||

| Line 16: | Line 16: | ||

|tech=CMOS | |tech=CMOS | ||

|package name 1=intel,fclga_3647 | |package name 1=intel,fclga_3647 | ||

| − | |predecessor= | + | |predecessor=Skylake SP |

| − | |predecessor link=intel/cores/ | + | |predecessor link=intel/cores/skylake sp |

|successor=Ice Lake SP | |successor=Ice Lake SP | ||

|successor link=intel/cores/ice lake sp | |successor link=intel/cores/ice lake sp | ||

| + | |contemporary=Cascade Lake SP | ||

| + | |contemporary link=intel/cores/cascade lake sp | ||

}} | }} | ||

'''Cascade Lake R''' ('''{{intel|Cascade Lake|l=arch}} Scalable Performance Refresh''') is code name for Intel's series of server [[multiprocessors]] based on the {{intel|Cascade Lake|l=arch}} microarchitecture as part of the {{intel|Purley|l=platform}} platform serving as mid-cycle refresh to {{intel|Cascade Lake SP|l=core}}. Cascade Lake R only targets mainstream entry and mid-range servers and therefore only support up to 2-way multiprocessing. As with {{\\|Cascade Lake SP}}, these chips also support up to [[28 cores]], incorporate {{x86|AVX512-VNNI|AVX512}} [[x86]] {{x86|extension}} for neural network / deep learning workloads, and introduces [[persistent memory]] support. Cascade Lake R-based chips are manufactured on an enhanced [[14 nm process]] and utilize the {{intel|Lewisburg|l=chipset}} chipset. | '''Cascade Lake R''' ('''{{intel|Cascade Lake|l=arch}} Scalable Performance Refresh''') is code name for Intel's series of server [[multiprocessors]] based on the {{intel|Cascade Lake|l=arch}} microarchitecture as part of the {{intel|Purley|l=platform}} platform serving as mid-cycle refresh to {{intel|Cascade Lake SP|l=core}}. Cascade Lake R only targets mainstream entry and mid-range servers and therefore only support up to 2-way multiprocessing. As with {{\\|Cascade Lake SP}}, these chips also support up to [[28 cores]], incorporate {{x86|AVX512-VNNI|AVX512}} [[x86]] {{x86|extension}} for neural network / deep learning workloads, and introduces [[persistent memory]] support. Cascade Lake R-based chips are manufactured on an enhanced [[14 nm process]] and utilize the {{intel|Lewisburg|l=chipset}} chipset. | ||

Cascade Lake R-based models are branded as the 2nd-generation {{intel|Xeon Bronze}}, {{intel|Xeon Silver}}, and {{intel|Xeon Gold}} [[processor families]]. | Cascade Lake R-based models are branded as the 2nd-generation {{intel|Xeon Bronze}}, {{intel|Xeon Silver}}, and {{intel|Xeon Gold}} [[processor families]]. | ||

| + | |||

| + | == Overview == | ||

| + | Cascade Lake R processors are based on Intel's {{intel|Cascade Lake|l=arch}} microarchitecture intended to enhance the original {{\\|Cascade Lake SP}} lineup. These processors introduce a significant price cut compared to original SKUs or additional cores and the higher frequency at comparable price. The intended purpose of this release is to elevate the performance-per-dollar for entry-level and mid-range server processors. | ||

| + | |||

| + | As with {{\\|Skylake SP}}, Cascade Lake SP processors utilize the new {{intel|FCLGA-3647}} package (which makes use of "Socket P"). Those use the {{intel|Lewisburg}} chipset ({{intel|Platform Controller Hub|HUB}}) via 4 PCIe3 lanes using Intel's proprietary {{intel|Direct Media Interface}} 3.0 (DMI 3.0), allowing for 8 GT/s transfer rate per lane. When in multi-socket configuration, the microprocessor is connected to the other processors via the {{intel|Ultra Path Interconnect}} (UPI) links which Intel introduced with Skylake SP as well, replacing and obsoleting the older {{intel|QuickPath Interconnect}} (QPI) operating. Depending on the model, there may be either two or three UPI links inter-linking each socket (for more details see {{intel|cascade lake#Scalability|Cascade Lake § Scalability|l=arch}}). | ||

| + | |||

| + | === Common Features === | ||

| + | All Cascade Lake R processors have the following: | ||

| + | |||

| + | * Hexa-channel memory | ||

| + | ** 1 TiB, 2 TiB medium memory support variants (''M'' suffix), and 4.5 TiB for extended memory variants (''L'' suffix) | ||

| + | ** UP to DDR4-2933 MT/s | ||

| + | ** [[ECC]] support | ||

| + | * '''TDP:''' 85 W to 205 W | ||

| + | * '''PCIe:''' x48 Lanes of PCIe Gen 3 | ||

| + | * '''ISA:''' Everything up to AVX-512 (SMM, FPU, NX, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, AES, AVX, FMA3, AVX2, AVX512F, AVX512CD, AVX512BW, AVX512DQ, AVX512VL, AVX512VNNI) | ||

| + | * '''Features:''' {{intel|Speed Shift}}, {{intel|vPro}}, {{intel|VT-x}}, {{intel|TSX}}, {{intel|TXT}}, {{intel|Volume Management Device}} (VMD), {{intel|Mode-based Execute Control}} (MBE), {{intel|Key Protection Technology}} (KPT), and {{intel|Platform Trust Technology}} (PTT). | ||

| + | ** Silver and up also have {{intel|Hyper-Threading}} and {{intel|Turbo Boost}} | ||

| + | ** Gold and up also have Node Controller Support and offer Integrated Omni-Path Fabric Interface options | ||

| + | |||

| + | {{clear}} | ||

| + | |||

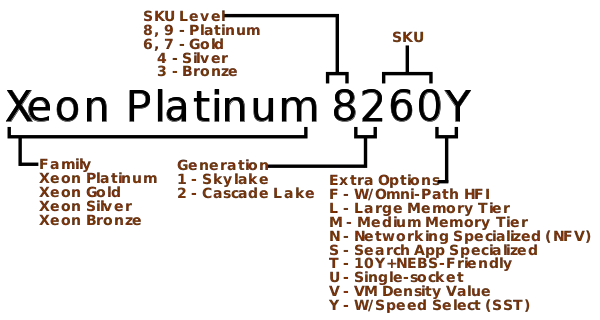

| + | === Naming Scheme === | ||

| + | Cascade Lake SKUs follow the following naming scheme. | ||

| + | |||

| + | :[[File:cascade lake naming scheme.svg|600px]] | ||

| + | |||

| + | Where, | ||

| + | |||

| + | * "''F''" suffix integrates the {{intel|Omni-Path}} Host Fabric Interface (HFI) die on-package | ||

| + | * "''L''" suffix indicates the SKU is a large memory (4.5 TiB) tier SKU | ||

| + | * "''M''" suffix indicates the SKU is a medium memory (2 TiB) tier SKU | ||

| + | * "''N''" suffix indicates the SKU is a networking-specialized model | ||

| + | * "''S''" suffix indicates the SKU is a search application-specialized model | ||

| + | * "''T''" suffix indicates that SKU has an extended lifetime (10 year use) guarantees and [[NEBS]]-friendly packing specification | ||

| + | * "''V''" suffix indicates the SKU targets the VM density value market | ||

| + | * "''Y''" suffix indicates the SKU has {{intel|Speed Select Technology}} (SST) | ||

| + | * "''U''" suffix indicates the SKU is a single-socket model (even if part of the [[Xeon Gold]] family that normally supports up two 4-way [[SMP]]) | ||

| + | * "''R''" suffix indicates the SKU is a dual-socket model (even if part of the [[Xeon Gold]] family that normally supports up two 4-way [[SMP]]) | ||

| + | |||

| + | == Cascade Lake R Processors == | ||

| + | <!-- NOTE: | ||

| + | This table is generated automatically from the data in the actual articles. | ||

| + | If a microprocessor is missing from the list, an appropriate article for it needs to be | ||

| + | created and tagged accordingly. | ||

| + | |||

| + | Missing a chip? please dump its name here: https://en.wikichip.org/wiki/WikiChip:wanted_chips | ||

| + | --> | ||

| + | {{comp table start}} | ||

| + | <table class="comptable sortable tc5 tc6 tc14"> | ||

| + | {{comp table header|main|12:List of Cascade Lake R-based Processors}} | ||

| + | {{comp table header|main|8:Main Processor|1:Cache|2:Memory}} | ||

| + | {{comp table header|cols|Family|Price|Launched|Cores|Threads|Frequency|Max Turbo|%TDP|L3$|Mem Type|Max Mem}} | ||

| + | {{comp table header|lsep|25:[[Multiprocessors]] (2-way)}} | ||

| + | {{#ask: [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[core name::Cascade Lake R]] [[max cpu count::2]] | ||

| + | |?full page name | ||

| + | |?model number | ||

| + | |?microprocessor family | ||

| + | |?release price | ||

| + | |?first launched | ||

| + | |?core count | ||

| + | |?thread count | ||

| + | |?base frequency#GHz | ||

| + | |?turbo frequency (1 core)#GHz | ||

| + | |?tdp | ||

| + | |?l3$ size | ||

| + | |?supported memory type | ||

| + | |?max memory#TiB | ||

| + | |format=template | ||

| + | |template=proc table 3 | ||

| + | |userparam=13 | ||

| + | |mainlabel=- | ||

| + | |limit=75 | ||

| + | |valuesep=, | ||

| + | |sort=model number | ||

| + | }} | ||

| + | {{comp table count|ask=[[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[core name::Cascade Lake R]]}} | ||

| + | </table> | ||

| + | {{comp table end}} | ||

| + | |||

| + | === SKU Comparison === | ||

| + | Below are a number of SKU comparison graphs based on their specifications. | ||

| + | |||

| + | <div style="float: left; margin: 10px"> | ||

| + | {{#ask: [[Category:microprocessor models by intel]] [[core name::Cascade Lake R]] | ||

| + | |?core count | ||

| + | |?base frequency | ||

| + | |charttitle=Cores vs. Base Frequency | ||

| + | |numbersaxislabel=Frequency (MHz) | ||

| + | |labelaxislabel=Core Count | ||

| + | |height=400 | ||

| + | |width=400 | ||

| + | |theme=vector | ||

| + | |group=property | ||

| + | |grouplabel=subject | ||

| + | |charttype=scatter | ||

| + | |format=jqplotseries | ||

| + | |mainlabel=- | ||

| + | }} | ||

| + | </div> | ||

| + | |||

| + | <div style="float: left; margin: 10px"> | ||

| + | {{#ask: [[Category:microprocessor models by intel]] [[core name::Cascade Lake R]] | ||

| + | |?core count | ||

| + | |?turbo frequency (1 core) | ||

| + | |charttitle=Cores vs. Turbo Frequency | ||

| + | |numbersaxislabel=Frequency (MHz) | ||

| + | |labelaxislabel=Core Count | ||

| + | |height=400 | ||

| + | |width=400 | ||

| + | |theme=vector | ||

| + | |group=property | ||

| + | |grouplabel=subject | ||

| + | |charttype=scatter | ||

| + | |format=jqplotseries | ||

| + | |mainlabel=- | ||

| + | }} | ||

| + | </div> | ||

| + | |||

| + | <div style="float: left; margin: 10px"> | ||

| + | {{#ask: [[Category:microprocessor models by intel]] [[core name::Cascade Lake R]] | ||

| + | |?core count | ||

| + | |?tdp | ||

| + | |charttitle=Cores vs. TDP | ||

| + | |numbersaxislabel=TDP (W) | ||

| + | |labelaxislabel=Core Count | ||

| + | |height=400 | ||

| + | |width=400 | ||

| + | |theme=vector | ||

| + | |group=property | ||

| + | |grouplabel=subject | ||

| + | |charttype=scatter | ||

| + | |format=jqplotseries | ||

| + | |mainlabel=- | ||

| + | }} | ||

| + | </div> | ||

| + | |||

| + | <div style="float: left; margin: 10px"> | ||

| + | {{#ask: [[Category:microprocessor models by intel]] [[core name::Cascade Lake R]] | ||

| + | |?turbo frequency (1 core) | ||

| + | |?tdp | ||

| + | |charttitle=Frequency vs. TDP | ||

| + | |numbersaxislabel=TDP (W) | ||

| + | |labelaxislabel=Frequency (MHz) | ||

| + | |height=400 | ||

| + | |width=400 | ||

| + | |theme=vector | ||

| + | |group=property | ||

| + | |grouplabel=subject | ||

| + | |charttype=scatter | ||

| + | |format=jqplotseries | ||

| + | |mainlabel=- | ||

| + | }} | ||

| + | </div> | ||

| + | |||

| + | {{clear}} | ||

| + | |||

| + | == See also == | ||

| + | {{intel cascade lake core see also}} | ||

Latest revision as of 11:25, 28 February 2020

| Edit Values | |

| Cascade Lake R | |

| |

| General Info | |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | February 24, 2020 (announced) February 24, 2020 (launched) |

| Microarchitecture | |

| ISA | x86-64 (x86) |

| Microarchitecture | Cascade Lake |

| Platform | Purley |

| Chipset | Lewisburg |

| Word Size | 8 octets 64 bit16 nibbles |

| Process | 14 nm 0.014 μm 1.4e-5 mm |

| Technology | CMOS |

| Packaging | |

| Package | FCLGA-3647 (FCLGA) |

| Dimension | 76.16 mm × 56.6 mm |

| Pitch | 0.8585 mm × 0.9906 mm |

| Contacts | 3647 |

| Socket | Socket P, LGA-3647 |

| Succession | |

| Contemporary | |

| Cascade Lake SP | |

Cascade Lake R (Cascade Lake Scalable Performance Refresh) is code name for Intel's series of server multiprocessors based on the Cascade Lake microarchitecture as part of the Purley platform serving as mid-cycle refresh to Cascade Lake SP. Cascade Lake R only targets mainstream entry and mid-range servers and therefore only support up to 2-way multiprocessing. As with Cascade Lake SP, these chips also support up to 28 cores, incorporate AVX512 x86 extension for neural network / deep learning workloads, and introduces persistent memory support. Cascade Lake R-based chips are manufactured on an enhanced 14 nm process and utilize the Lewisburg chipset.

Cascade Lake R-based models are branded as the 2nd-generation Xeon Bronze, Xeon Silver, and Xeon Gold processor families.

Contents

Overview[edit]

Cascade Lake R processors are based on Intel's Cascade Lake microarchitecture intended to enhance the original Cascade Lake SP lineup. These processors introduce a significant price cut compared to original SKUs or additional cores and the higher frequency at comparable price. The intended purpose of this release is to elevate the performance-per-dollar for entry-level and mid-range server processors.

As with Skylake SP, Cascade Lake SP processors utilize the new FCLGA-3647 package (which makes use of "Socket P"). Those use the Lewisburg chipset (HUB) via 4 PCIe3 lanes using Intel's proprietary Direct Media Interface 3.0 (DMI 3.0), allowing for 8 GT/s transfer rate per lane. When in multi-socket configuration, the microprocessor is connected to the other processors via the Ultra Path Interconnect (UPI) links which Intel introduced with Skylake SP as well, replacing and obsoleting the older QuickPath Interconnect (QPI) operating. Depending on the model, there may be either two or three UPI links inter-linking each socket (for more details see Cascade Lake § Scalability).

Common Features[edit]

All Cascade Lake R processors have the following:

- Hexa-channel memory

- 1 TiB, 2 TiB medium memory support variants (M suffix), and 4.5 TiB for extended memory variants (L suffix)

- UP to DDR4-2933 MT/s

- ECC support

- TDP: 85 W to 205 W

- PCIe: x48 Lanes of PCIe Gen 3

- ISA: Everything up to AVX-512 (SMM, FPU, NX, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, AES, AVX, FMA3, AVX2, AVX512F, AVX512CD, AVX512BW, AVX512DQ, AVX512VL, AVX512VNNI)

- Features: Speed Shift, vPro, VT-x, TSX, TXT, Volume Management Device (VMD), Mode-based Execute Control (MBE), Key Protection Technology (KPT), and Platform Trust Technology (PTT).

- Silver and up also have Hyper-Threading and Turbo Boost

- Gold and up also have Node Controller Support and offer Integrated Omni-Path Fabric Interface options

Naming Scheme[edit]

Cascade Lake SKUs follow the following naming scheme.

Where,

- "F" suffix integrates the Omni-Path Host Fabric Interface (HFI) die on-package

- "L" suffix indicates the SKU is a large memory (4.5 TiB) tier SKU

- "M" suffix indicates the SKU is a medium memory (2 TiB) tier SKU

- "N" suffix indicates the SKU is a networking-specialized model

- "S" suffix indicates the SKU is a search application-specialized model

- "T" suffix indicates that SKU has an extended lifetime (10 year use) guarantees and NEBS-friendly packing specification

- "V" suffix indicates the SKU targets the VM density value market

- "Y" suffix indicates the SKU has Speed Select Technology (SST)

- "U" suffix indicates the SKU is a single-socket model (even if part of the Xeon Gold family that normally supports up two 4-way SMP)

- "R" suffix indicates the SKU is a dual-socket model (even if part of the Xeon Gold family that normally supports up two 4-way SMP)

Cascade Lake R Processors[edit]

| List of Cascade Lake R-based Processors | |||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Main Processor | Cache | Memory | |||||||||||||||||||||||

| Model | Family | Price | Launched | Cores | Threads | Frequency | Max Turbo | TDP | L3$ | Mem Type | Max Mem | ||||||||||||||

| Multiprocessors (2-way) | |||||||||||||||||||||||||

| 4210R | Xeon Silver | $ 511.00 € 459.90 , $ 501.00£ 413.91 ¥ 52,801.63 € 450.90 £ 405.81 ¥ 51,768.33 | 24 February 2020 | 10 | 20 | 2.4 GHz 2,400 MHz 2,400,000 kHz | 3.2 GHz 3,200 MHz 3,200,000 kHz | 100 W 100,000 mW 0.134 hp 0.1 kW | 13.75 MiB 14,080 KiB 14,417,920 B 0.0134 GiB | DDR4-2400 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 4214R | Xeon Silver | $ 705.00 € 634.50 , $ 694.00£ 571.05 ¥ 72,847.65 € 624.60 £ 562.14 ¥ 71,711.02 | 24 February 2020 | 12 | 24 | 2.4 GHz 2,400 MHz 2,400,000 kHz | 3.5 GHz 3,500 MHz 3,500,000 kHz | 100 W 100,000 mW 0.134 hp 0.1 kW | 16.5 MiB 16,896 KiB 17,301,504 B 0.0161 GiB | DDR4-2400 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 4215R | Xeon Silver | $ 794.00 € 714.60 £ 643.14 ¥ 82,044.02 | 24 February 2020 | 8 | 16 | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 130 W 130,000 mW 0.174 hp 0.13 kW | 11 MiB 11,264 KiB 11,534,336 B 0.0107 GiB | DDR4-2400 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 5218R | Xeon Gold | $ 1,273.00 € 1,145.70 , $ 1,280.00£ 1,031.13 ¥ 131,539.09 € 1,152.00 £ 1,036.80 ¥ 132,262.40 | 24 February 2020 | 20 | 40 | 2.1 GHz 2,100 MHz 2,100,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 125 W 125,000 mW 0.168 hp 0.125 kW | 27.5 MiB 28,160 KiB 28,835,840 B 0.0269 GiB | DDR4-2666 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 5220R | Xeon Gold | $ 1,555.00 € 1,399.50 , $ 1,561.00£ 1,259.55 ¥ 160,678.15 € 1,404.90 £ 1,264.41 ¥ 161,298.13 | 24 February 2020 | 24 | 48 | 2.2 GHz 2,200 MHz 2,200,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 150 W 150,000 mW 0.201 hp 0.15 kW | 35.75 MiB 36,608 KiB 37,486,592 B 0.0349 GiB | DDR4-2666 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 6226R | Xeon Gold | $ 1,300.00 € 1,170.00 , $ 1,306.00£ 1,053.00 ¥ 134,329.00 € 1,175.40 £ 1,057.86 ¥ 134,948.98 | 24 February 2020 | 16 | 32 | 2.9 GHz 2,900 MHz 2,900,000 kHz | 3.9 GHz 3,900 MHz 3,900,000 kHz | 150 W 150,000 mW 0.201 hp 0.15 kW | 22 MiB 22,528 KiB 23,068,672 B 0.0215 GiB | DDR4-2933 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 6230R | Xeon Gold | $ 1,900.00 € 1,710.00 , $ 1,894.00£ 1,539.00 ¥ 196,327.00 € 1,704.60 £ 1,534.14 ¥ 195,707.02 | 24 February 2020 | 26 | 52 | 2.1 GHz 2,100 MHz 2,100,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 150 W 150,000 mW 0.201 hp 0.15 kW | 35.75 MiB 36,608 KiB 37,486,592 B 0.0349 GiB | DDR4-2933 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 6238R | Xeon Gold | $ 2,612.00 € 2,350.80 , $ 2,618.00£ 2,115.72 ¥ 269,897.96 € 2,356.20 £ 2,120.58 ¥ 270,517.94 | 24 February 2020 | 28 | 56 | 2.2 GHz 2,200 MHz 2,200,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 165 W 165,000 mW 0.221 hp 0.165 kW | 38.5 MiB 39,424 KiB 40,370,176 B 0.0376 GiB | DDR4-2933 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 6240R | Xeon Gold | $ 2,200.00 € 1,980.00 , $ 2,205.00£ 1,782.00 ¥ 227,326.00 € 1,984.50 £ 1,786.05 ¥ 227,842.65 | 24 February 2020 | 24 | 48 | 2.4 GHz 2,400 MHz 2,400,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 165 W 165,000 mW 0.221 hp 0.165 kW | 35.75 MiB 36,608 KiB 37,486,592 B 0.0349 GiB | DDR4-2933 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 6242R | Xeon Gold | $ 2,529.00 € 2,276.10 £ 2,048.49 ¥ 261,321.57 | 24 February 2020 | 20 | 40 | 3.1 GHz 3,100 MHz 3,100,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | 205 W 205,000 mW 0.275 hp 0.205 kW | 35.75 MiB 36,608 KiB 37,486,592 B 0.0349 GiB | DDR4-2933 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 6246R | Xeon Gold | $ 3,286.00 € 2,957.40 £ 2,661.66 ¥ 339,542.38 | 24 February 2020 | 16 | 32 | 3.4 GHz 3,400 MHz 3,400,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | 205 W 205,000 mW 0.275 hp 0.205 kW | 35.75 MiB 36,608 KiB 37,486,592 B 0.0349 GiB | DDR4-2933 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 6248R | Xeon Gold | $ 2,700.00 € 2,430.00 £ 2,187.00 ¥ 278,991.00 | 24 February 2020 | 24 | 48 | 3 GHz 3,000 MHz 3,000,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 205 W 205,000 mW 0.275 hp 0.205 kW | 35.75 MiB 36,608 KiB 37,486,592 B 0.0349 GiB | DDR4-2933 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| 6258R | Xeon Gold | $ 3,950.00 € 3,555.00 £ 3,199.50 ¥ 408,153.50 | 24 February 2020 | 28 | 56 | 2.7 GHz 2,700 MHz 2,700,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 205 W 205,000 mW 0.275 hp 0.205 kW | 38.5 MiB 39,424 KiB 40,370,176 B 0.0376 GiB | DDR4-2933 | 1 TiB 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB | ||||||||||||||

| Count: 13 | |||||||||||||||||||||||||

SKU Comparison[edit]

Below are a number of SKU comparison graphs based on their specifications.

See also[edit]

|

• Power

• Performance |

| chipset | Lewisburg + |

| designer | Intel + |

| first announced | February 24, 2020 + |

| first launched | February 24, 2020 + |

| instance of | core + |

| isa | x86-64 + |

| isa family | x86 + |

| main image |  + + |

| manufacturer | Intel + |

| microarchitecture | Cascade Lake + |

| name | Cascade Lake R + |

| package | FCLGA-3647 + |

| platform | Purley + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| socket | Socket P + and LGA-3647 + |

| technology | CMOS + |

| word size | 64 bit (8 octets, 16 nibbles) + |