(→Die) |

|||

| (10 intermediate revisions by the same user not shown) | |||

| Line 17: | Line 17: | ||

|predecessor link=phytium/microarchitectures/mars_i | |predecessor link=phytium/microarchitectures/mars_i | ||

}} | }} | ||

| − | '''Mars II''' is the successor to {{\\|Mars I}}, an [[ARM]] server SoC microarchitecture designed by [[Phytium Technology]] for the Chinese server market. | + | '''Mars II''' is the successor to {{\\|Mars I}}, an [[ARM]] server SoC microarchitecture designed by [[Phytium Technology]] for the [[Chinese]] server market. |

== Process technology == | == Process technology == | ||

| − | {{ | + | Mars II is largely a shrink of {{\\|Mars I}}, from [[28 nm process]] to a [[16 nm|16 nm FinFET process]]. |

== Architecture == | == Architecture == | ||

| − | {{ | + | === Key changes from {{\\|Mars I}} === |

| + | * [[16 nm process]] (from [[28 nm]]) | ||

| + | * 15% higher frequency (2.3 GHz, up from 2 GHz) | ||

| + | ** higher [[FLOPS]] performance (588.8 GFLOPS, up from 512 GFLOPS) | ||

| + | * -25% lower power (96 W [[TDP]], down from 120 W) | ||

| + | * Core | ||

| + | ** FTC-662 (from FTC-661/0) | ||

| + | * System memory | ||

| + | ** Panel directly connected to 1 MCU (Previously linked to CMC) | ||

| + | *** [[DDR4]] (from [[DDR3]]) | ||

| + | *** Higher data rates (2400 MT/s, up from 1600 MT/s) | ||

| + | {{expand list}} | ||

| + | |||

| + | == Block diagram == | ||

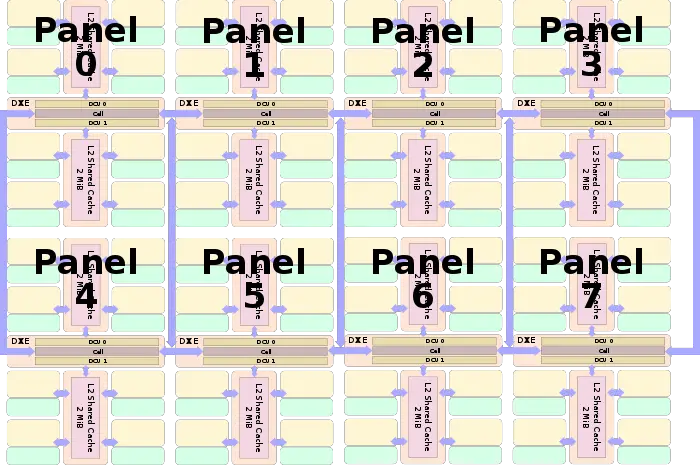

| + | === Entire SoC === | ||

| + | :[[File:mars ii soc block diagram.svg|700px]] | ||

| + | |||

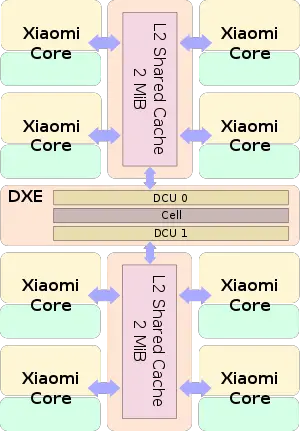

| + | === Panel === | ||

| + | :[[File:mars ii panel block diagram.svg|300px]] | ||

| + | |||

| + | === Core === | ||

| + | {{main|phytium/microarchitectures/xiaomi|l1=Xiaomi Core}} | ||

| + | See {{\\|Xiaomi|Xiaomi Core}}. | ||

== Overview == | == Overview == | ||

| − | + | Mars II is Phytium's second-generation [[many-core]] server processor based on a custom [[ARM]] core. The Mars II is largely a shrink of their first-generation SoC but it does introduce a number of enhancements. Fabricated on a leading-edge [[16 nm|16 nm FinFET process]], the new SoC is considerably smaller than the prior die, offers higher frequency, and lower power. Mars II features [[64 cores|64]] custom [[ARMv8.0]] cores operating at up to 2.3 GHz for a total of 588.8 [[GFLOPS]]. The SoC incorporates high DDR4-2400 memory channels and includes 33 PCIe Gen 3.0 lanes. | |

| + | |||

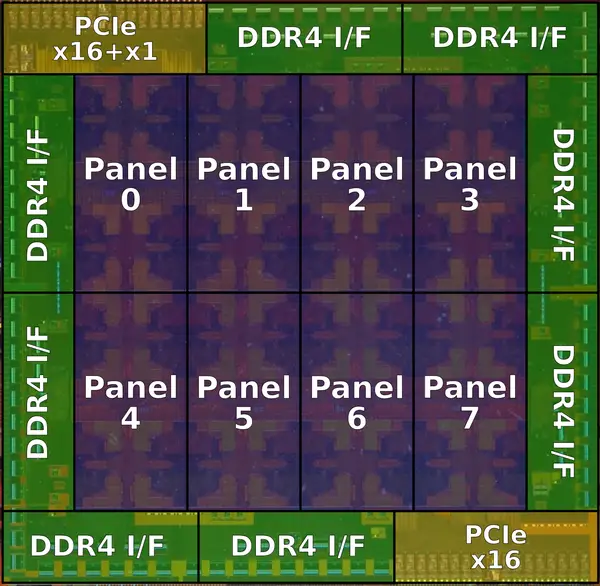

| + | == Package == | ||

| + | <table class="wikitable"> | ||

| + | <tr><th>Package</th><td>FCBGA-3576</td><td rowspan="4">[[File:mars ii fcbga-3576.png|400px]]</td></tr> | ||

| + | <tr><th>Dimensions</th><td>61mm x 61mm</td></tr> | ||

| + | <tr><th>Bumps</th><td>11916</td></tr> | ||

| + | <tr><th>Contacts</th><td>3576</td></tr> | ||

| + | </table> | ||

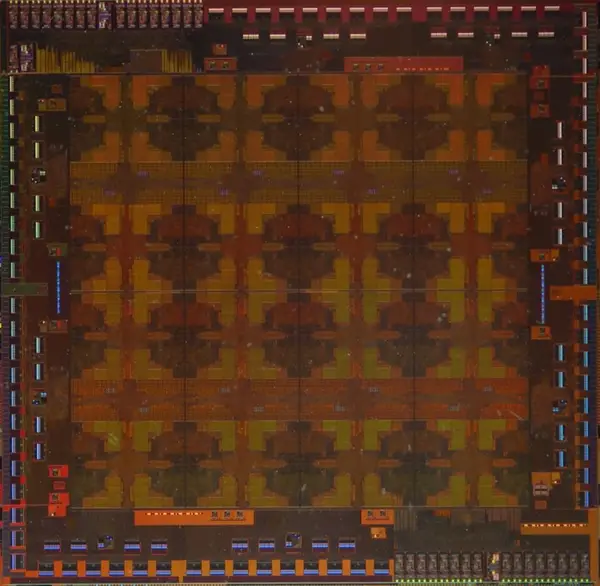

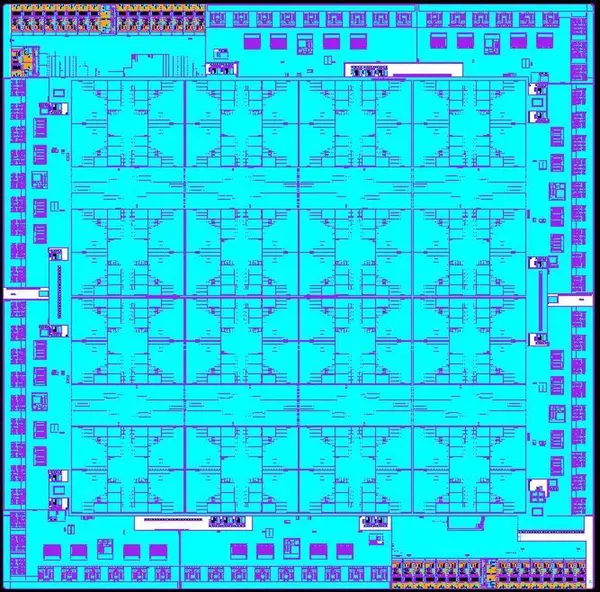

== Die == | == Die == | ||

| + | === Panel === | ||

| + | <div> | ||

| + | <div style="float: left;">[[File:mars ii panel.png|200px]]</div> | ||

| + | <div style="float: left;">[[File:mars ii panel (annotated).png|200px]]</div> | ||

| + | </div> | ||

| + | |||

| + | {{clear}} | ||

| + | === SoC === | ||

* [[16 nm process]] (16FF+) GL | * [[16 nm process]] (16FF+) GL | ||

* 1 [[polysilicon layer|Poly]], 11 [[Metal layers]], [[RDL]] | * 1 [[polysilicon layer|Poly]], 11 [[Metal layers]], [[RDL]] | ||

* 6,000,000,000 [[transistors]] | * 6,000,000,000 [[transistors]] | ||

* 370 mm² [[die size]] | * 370 mm² [[die size]] | ||

| + | * 2.3 GHz @ 0.9 V, 96 W | ||

| Line 42: | Line 81: | ||

:[[File:mars ii die 2.png|600px]] | :[[File:mars ii die 2.png|600px]] | ||

| + | |||

| + | == All Mars II Processors == | ||

| + | <!-- NOTE: | ||

| + | This table is generated automatically from the data in the actual articles. | ||

| + | If a microprocessor is missing from the list, an appropriate article for it needs to be | ||

| + | created and tagged accordingly. | ||

| + | |||

| + | Missing a chip? please dump its name here: https://en.wikichip.org/wiki/WikiChip:wanted_chips | ||

| + | --> | ||

| + | {{comp table start}} | ||

| + | <table class="comptable sortable tc4"> | ||

| + | {{comp table header|main|6:List of Mars II-based Processors}} | ||

| + | {{comp table header|cols|Launched|Cores|L2|%Frequency|%TDP}} | ||

| + | {{#ask: [[Category:microprocessor models by phytium]] [[microarchitecture::Mars II]] | ||

| + | |?full page name | ||

| + | |?model number | ||

| + | |?first launched | ||

| + | |?core count | ||

| + | |?l2$ size | ||

| + | |?base frequency#GHz | ||

| + | |?tdp#W | ||

| + | |format=template | ||

| + | |template=proc table 3 | ||

| + | |userparam=7 | ||

| + | |mainlabel=- | ||

| + | }} | ||

| + | {{comp table count|ask=[[Category:microprocessor models by phytium]] [[microarchitecture::Mars II]]}} | ||

| + | </table> | ||

| + | {{comp table end}} | ||

| + | |||

| + | == Bibliography == | ||

| + | * HPC Asia 2019 | ||

Latest revision as of 14:23, 26 March 2019

| Edit Values | |

| Mars II µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Phytium |

| Manufacturer | TSMC |

| Introduction | 2019 |

| Process | 16 nm |

| Core Configs | 64 |

| Pipeline | |

| Type | Superscalar, Pipelined |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | ARMv8 |

| Succession | |

Mars II is the successor to Mars I, an ARM server SoC microarchitecture designed by Phytium Technology for the Chinese server market.

Contents

Process technology[edit]

Mars II is largely a shrink of Mars I, from 28 nm process to a 16 nm FinFET process.

Architecture[edit]

Key changes from Mars I[edit]

- 16 nm process (from 28 nm)

- 15% higher frequency (2.3 GHz, up from 2 GHz)

- higher FLOPS performance (588.8 GFLOPS, up from 512 GFLOPS)

- -25% lower power (96 W TDP, down from 120 W)

- Core

- FTC-662 (from FTC-661/0)

- System memory

This list is incomplete; you can help by expanding it.

Block diagram[edit]

Entire SoC[edit]

Panel[edit]

Core[edit]

- Main article: Xiaomi Core

See Xiaomi Core.

Overview[edit]

Mars II is Phytium's second-generation many-core server processor based on a custom ARM core. The Mars II is largely a shrink of their first-generation SoC but it does introduce a number of enhancements. Fabricated on a leading-edge 16 nm FinFET process, the new SoC is considerably smaller than the prior die, offers higher frequency, and lower power. Mars II features 64 custom ARMv8.0 cores operating at up to 2.3 GHz for a total of 588.8 GFLOPS. The SoC incorporates high DDR4-2400 memory channels and includes 33 PCIe Gen 3.0 lanes.

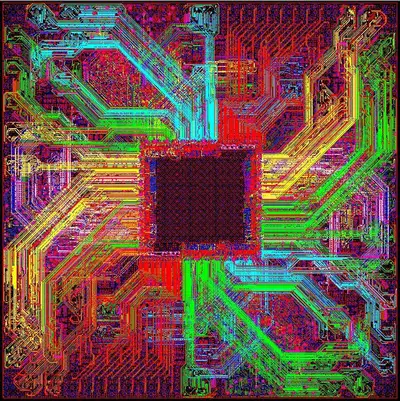

Package[edit]

| Package | FCBGA-3576 |  |

|---|---|---|

| Dimensions | 61mm x 61mm | |

| Bumps | 11916 | |

| Contacts | 3576 |

Die[edit]

Panel[edit]

SoC[edit]

- 16 nm process (16FF+) GL

- 1 Poly, 11 Metal layers, RDL

- 6,000,000,000 transistors

- 370 mm² die size

- 2.3 GHz @ 0.9 V, 96 W

All Mars II Processors[edit]

| List of Mars II-based Processors | ||||||

|---|---|---|---|---|---|---|

| Model | Launched | Cores | L2 | Frequency | TDP | |

| FT-2000+/64 | 2019 | 64 | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 96 W 96,000 mW 0.129 hp 0.096 kW | |

| Count: 1 | ||||||

Bibliography[edit]

- HPC Asia 2019

| codename | Mars II + |

| core count | 64 + |

| designer | Phytium + |

| first launched | 2019 + |

| full page name | phytium/microarchitectures/mars ii + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Mars II + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |