From WikiChip

Difference between revisions of "intel/microarchitectures/knights hill"

(hill) |

|||

| (13 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

{{intel title|Knights Hill|arch}} | {{intel title|Knights Hill|arch}} | ||

| − | '''Knights Hill''' was | + | {{microarchitecture |

| + | |atype=CPU | ||

| + | |name=Knights Hill | ||

| + | |designer=Intel | ||

| + | |manufacturer=Intel | ||

| + | |process=10 nm | ||

| + | |type=Superscalar | ||

| + | |oooe=Yes | ||

| + | |speculative=Yes | ||

| + | |renaming=Yes | ||

| + | |isa=x86-16 | ||

| + | |isa 2=x86-32 | ||

| + | |isa 3=x86-64 | ||

| + | |predecessor=Knights Landing | ||

| + | |predecessor link=intel/microarchitectures/knights_landing | ||

| + | |successor=Knights Peak | ||

| + | |successor link=intel/microarchitectures/knights_peak | ||

| + | }} | ||

| + | '''Knights Hill''' ('''KNH''') was a planned successor to {{\\|Knights Landing}}, a [[10 nm]] [[many-core]] microarchitecture designed by [[intel]] for high performance computing. | ||

| + | |||

| + | == History == | ||

| + | [[File:XeonPhiGenerations.jpg|right|500px]] | ||

| + | Announced in 2014, Knights Hill was originally planned to be delivered in 2016 and be manufactured on a [[10 nm process]]. The architecture was also planned to power a number of supercomputers, including the United States highest-performance supercomputer, [[aurora (supercomputer)|Aurora]]. Delays with [[10 nm]] has pushed the product back to 2017. Eventually, in November 2017 Intel announced that Knights Hill would be cancelled: | ||

| + | |||

| + | <blockquote>One step we’re taking is to replace one of the future Intel® Xeon Phi™ processors (code name Knights Hill) with a new platform and new microarchitecture specifically designed for exascale.</blockquote> | ||

| + | |||

| + | == Brands == | ||

| + | Knights Hill was branded as 3rd generation {{intel|Xeon Phi}} | ||

| + | |||

| + | == Process Technology == | ||

| + | Knights Hill was intended to be fabricated on Intel's [[10 nm process]]. | ||

| + | |||

| + | == Architecture == | ||

| + | Intel released very few architectural details regarding Knights Hill. | ||

| + | |||

| + | === Key changes from {{\\|Knights Landing}} === | ||

| + | * [[10 nm]] (from [[14 nm]]) | ||

| + | * 2nd Generation {{intel|Omni-Path|Omni-Path Architecture}} | ||

| + | |||

| + | == References == | ||

| + | * [https://itpeernetwork.intel.com/unleashing-high-performance-computing/ Unleashing High-Performance Computing Today and Tomorrow], November 13, 2017 | ||

Latest revision as of 16:26, 8 April 2018

| Edit Values | |

| Knights Hill µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Process | 10 nm |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | x86-16, x86-32, x86-64 |

| Succession | |

Knights Hill (KNH) was a planned successor to Knights Landing, a 10 nm many-core microarchitecture designed by intel for high performance computing.

Contents

History[edit]

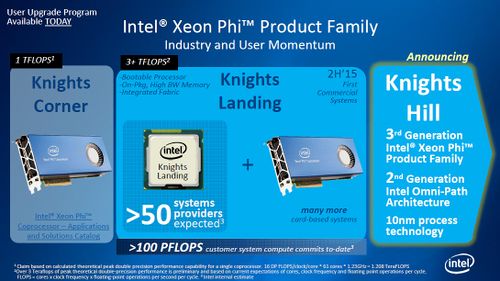

Announced in 2014, Knights Hill was originally planned to be delivered in 2016 and be manufactured on a 10 nm process. The architecture was also planned to power a number of supercomputers, including the United States highest-performance supercomputer, Aurora. Delays with 10 nm has pushed the product back to 2017. Eventually, in November 2017 Intel announced that Knights Hill would be cancelled:

One step we’re taking is to replace one of the future Intel® Xeon Phi™ processors (code name Knights Hill) with a new platform and new microarchitecture specifically designed for exascale.

Brands[edit]

Knights Hill was branded as 3rd generation Xeon Phi

Process Technology[edit]

Knights Hill was intended to be fabricated on Intel's 10 nm process.

Architecture[edit]

Intel released very few architectural details regarding Knights Hill.

Key changes from Knights Landing[edit]

- 10 nm (from 14 nm)

- 2nd Generation Omni-Path Architecture

References[edit]

- Unleashing High-Performance Computing Today and Tomorrow, November 13, 2017

Facts about "Knights Hill - Microarchitectures - Intel"

| codename | Knights Hill + |

| designer | Intel + |

| full page name | intel/microarchitectures/knights hill + |

| instance of | microarchitecture + |

| instruction set architecture | x86-16 +, x86-32 + and x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Knights Hill + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |