From WikiChip

Difference between revisions of "samsung/microarchitectures/m2"

m |

|||

| Line 35: | Line 35: | ||

! Compiler !! Arch-Specific || Arch-Favorable | ! Compiler !! Arch-Specific || Arch-Favorable | ||

|- | |- | ||

| − | | [[GCC]] || <code>-march=armv8-a+crypto</code> || <code>-mtune=exynos- | + | | [[GCC]] || <code>-march=armv8-a+crypto</code> || <code>-mtune=exynos-m2</code> |

|} | |} | ||

Revision as of 03:04, 5 February 2018

| Edit Values | |

| Mongoose 2 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Samsung |

| Manufacturer | Samsung |

| Process | 10 nm |

| Pipeline | |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Decode | 4-way |

| Instructions | |

| ISA | ARMv8 |

| Cache | |

| L1I Cache | 64 KiB/core 4-way set associative |

| L1D Cache | 32 KiB/core 8-way set associative |

| L2 Cache | 2 MiB/cluster 16-way set associative |

| Succession | |

Mongoose 2 (M2) is an ARM microarchitecture designed by Samsung for their consumer electronics serving as a successor to the Mongoose 1.

Contents

Process Technology

M2 was fabricated on Samsung's first generation 10LPE (Low Power Early) process.

Compiler support

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| GCC | -march=armv8-a+crypto |

-mtune=exynos-m2

|

Architecture

Key changes from Mongoose 1

- 10nm 10LPE process (from 14 nm)

This list is incomplete; you can help by expanding it.

Block Diagram

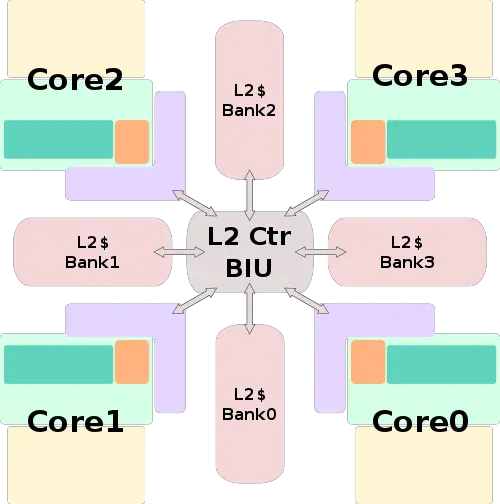

Core Cluster Overview

(Cluster identical to Mongoose 1)

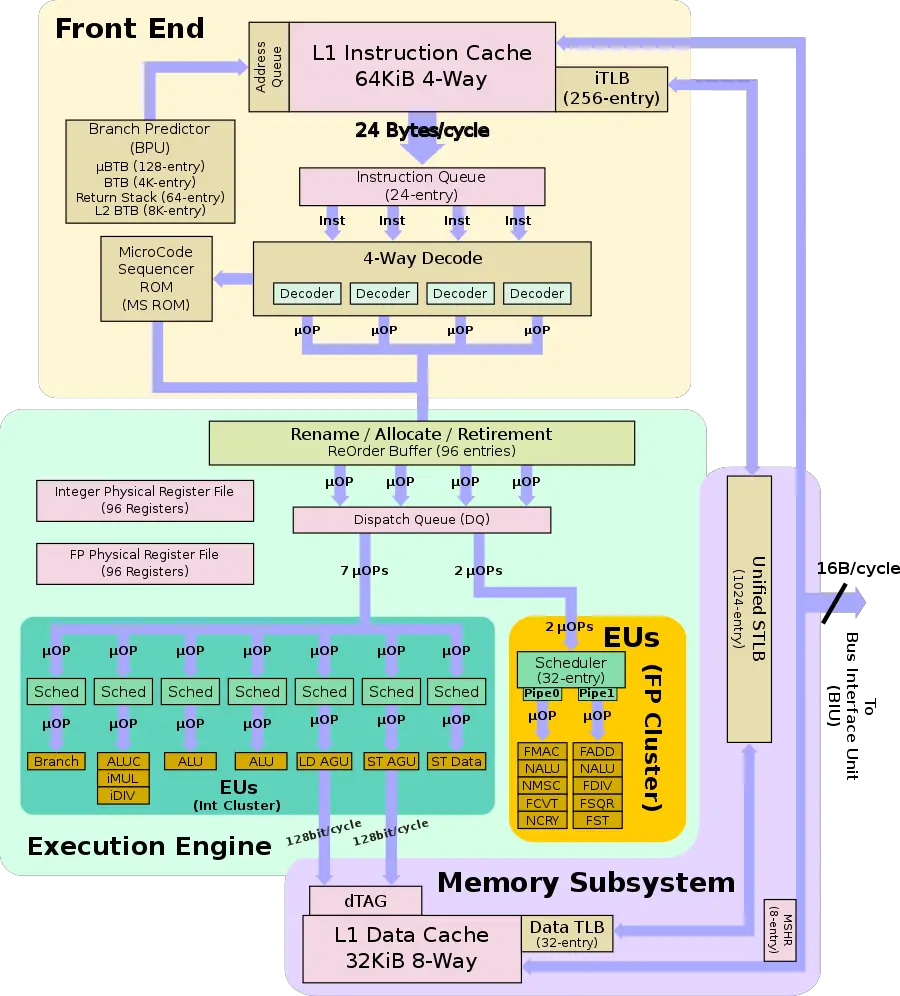

Individual Core

(Core identical to Mongoose 1)

Memory Hierarchy

- Cache

- L1I Cache

- 64 KiB, 4-way set associative

- 128 B line size

- per core

- Parity-protected

- 64 KiB, 4-way set associative

- L1D Cache

- 32 KiB, 8-way set associative

- 64 B line size

- per core

- 4 cycles for fastest load-to-use

- 16 B/cycle load bandwidth

- 16 B/cycle store bandwidth

- 32 KiB, 8-way set associative

- L2 Cache

- 2 MiB, 16-way set associative

- 4x banks (512 KiB each)

- Inclusive of L1

- 22 cycles latency

- 16 B/cycle/CPU bandwidth

- 2 MiB, 16-way set associative

- L1I Cache

Mongoose 1 TLB consists of dedicated L1 TLB for instruction cache (ITLB) and another one for data cache (DTLB). Additionally there is a unified L2 TLB (STLB).

- TLBs

- ITLB

- 256-entry

- DTLB

- 32-entry

- STLB

- 1,024-entry

- Per core

- ITLB

- BPU

- 4K-entry main BTB

- 64-entry µBTB

- 64-entry return stack

Core

The M2 core appears to be fairly identical to the M1.

All M2 Processors

| List of M2-based Processors | ||||||||

|---|---|---|---|---|---|---|---|---|

| Main processor | Integrated Graphics | |||||||

| Model | Family | Launched | Arch | Cores | Frequency | Turbo | GPU | Frequency |

| Count: 0 | ||||||||

Facts about "Exynos M2 - Microarchitectures - Samsung"

| codename | Mongoose 2 + |

| designer | Samsung + |

| full page name | samsung/microarchitectures/m2 + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8 + |

| manufacturer | Samsung + |

| microarchitecture type | CPU + |

| name | Mongoose 2 + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |