From WikiChip

Difference between revisions of "amd/duron/dhd1200amt1b"

(initial) |

m (Bot: moving all {{mpu}} to {{chip}}) |

||

| (15 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{amd title|Duron 1200 (Morgan)}} | {{amd title|Duron 1200 (Morgan)}} | ||

| − | {{ | + | {{chip |

| name = Duron 1200 | | name = Duron 1200 | ||

| − | | no image = | + | | no image = |

| − | | image = | + | | image = Amd-duron-1200.jpg |

| − | | image size = | + | | image size = 250px |

| caption = | | caption = | ||

| designer = AMD | | designer = AMD | ||

| Line 10: | Line 10: | ||

| model number = Duron 1200 | | model number = Duron 1200 | ||

| part number = DHD1200AMT1B | | part number = DHD1200AMT1B | ||

| − | |||

| part number 2 = | | part number 2 = | ||

| part number 3 = | | part number 3 = | ||

| + | | part number 4 = | ||

| market = Desktop | | market = Desktop | ||

| first announced = November 15, 2001 | | first announced = November 15, 2001 | ||

| Line 45: | Line 45: | ||

| thread count = 1 | | thread count = 1 | ||

| max cpus = 1 | | max cpus = 1 | ||

| − | | max memory = 4 | + | | max memory = 4 GiB |

| + | |||

| − | |||

| power = | | power = | ||

| v core = 1.75 V | | v core = 1.75 V | ||

| Line 79: | Line 79: | ||

| socket 0 type = PGA-462 | | socket 0 type = PGA-462 | ||

}} | }} | ||

| + | The '''Duron 1200''' based on the {{amd|Morgan|l=core}} core was a {{arch|32}} [[x86]] [[microprocessor]] developed by [[AMD]] and introduced in late 2001. This model was part of the second generation of the {{amd|Duron}} family. Designed based on AMD's {{amd|microarchitecture/k7|K7}} (a {{amd|Thunderbird}}-derivative) on a [[180 nm process]], this MPU operated at 1200 MHz with a bus capable of 200 MT/s with a max TDP of 54.7 W and a typical TDP of 50.3 W. | ||

| + | |||

| + | == Cache == | ||

| + | {{main|amd/microarchitectures/k7#Memory_Hierarchy|l1=K7 § Cache}} | ||

| + | {{cache info | ||

| + | |l1i cache=64 KiB | ||

| + | |l1i break=1x64 KiB | ||

| + | |l1i desc=2-way set associative | ||

| + | |l1i extra= | ||

| + | |l1d cache=64 KiB | ||

| + | |l1d break=1x64 KiB | ||

| + | |l1d desc=2-way set associative | ||

| + | |l1d extra= | ||

| + | |l2 cache=64 KiB | ||

| + | |l2 break=1x64 KiB | ||

| + | |l2 desc=16-way set associative | ||

| + | |l2 extra= | ||

| + | |l3 cache= | ||

| + | |l3 break= | ||

| + | |l3 desc= | ||

| + | |l3 extra= | ||

| + | }} | ||

| + | |||

| + | == Graphics == | ||

| + | This SoC has no integrated graphics processing unit. | ||

| + | |||

| + | == Features == | ||

| + | {{x86 features | ||

| + | | em64t = | ||

| + | | nx = | ||

| + | | txt = | ||

| + | | tsx = | ||

| + | | vpro = | ||

| + | | ht = | ||

| + | | tbt1 = | ||

| + | | tbt2 = | ||

| + | | bpt = | ||

| + | | vt-x = | ||

| + | | vt-d = | ||

| + | | ept = | ||

| + | | mmx = Yes | ||

| + | | emmx = Yes | ||

| + | | 3dnow = Yes | ||

| + | | e3dnow = Yes | ||

| + | | sse = | ||

| + | | sse2 = | ||

| + | | sse3 = | ||

| + | | ssse3 = | ||

| + | | sse4 = | ||

| + | | sse4.1 = | ||

| + | | sse4.2 = | ||

| + | | aes = | ||

| + | | pclmul = | ||

| + | | avx = | ||

| + | | avx2 = | ||

| + | | bmi = | ||

| + | | bmi1 = | ||

| + | | bmi2 = | ||

| + | | f16c = | ||

| + | | fma3 = | ||

| + | | mpx = | ||

| + | | sgx = | ||

| + | | eist = | ||

| + | }} | ||

| + | * [[has feature::Halt State]] | ||

| + | * [[has feature::Sleep State]] | ||

| + | == Documents == | ||

| + | === DataSheet === | ||

| + | * [[:File:AMD Duron Processor Model 7 Data Sheet (January, 2002).pdf|AMD Duron Processor Model 7 Data Sheet]]; Publication # 24310; Rev: G; Issue Date: January 2002. | ||

| + | === Other === | ||

| + | * [[:File:AMD Duron Processor Model 7 Revision Guid (October, 2003).pdf|AMD Duron Processor Model 7 Revision Guide]]; Publication # 24806; Rev: E; Issue Date: October 2003. | ||

| + | |||

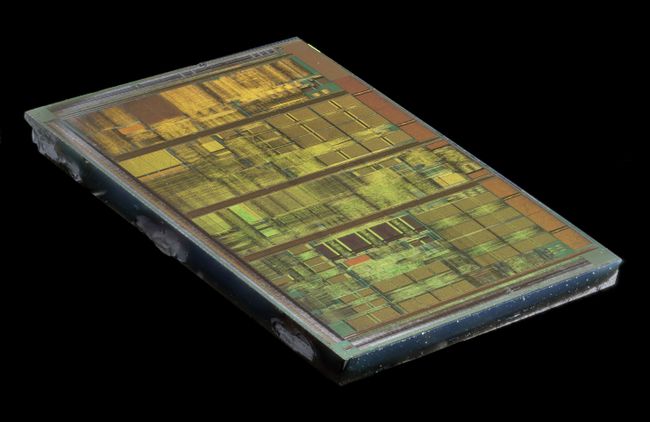

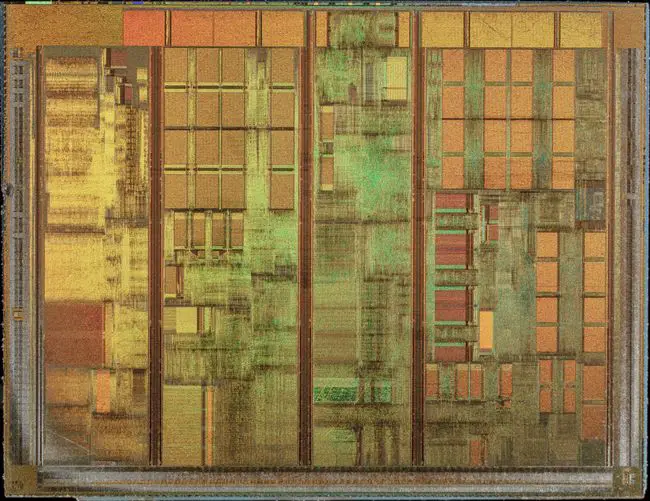

| + | == Die Shot == | ||

| + | [[File:AMD DHD1200AMT1B die shot.jpg|650px]] | ||

| + | |||

| + | |||

| + | [[File:AMD DHD1200AMT1B die shot 2.jpg|650px]] | ||

| + | |||

| + | == See also == | ||

| + | * {{amd|Duron}} | ||

| + | * {{intel|Celeron}} | ||

Latest revision as of 15:07, 13 December 2017

| Edit Values | |

| Duron 1200 | |

| |

| General Info | |

| Designer | AMD |

| Manufacturer | AMD |

| Model Number | Duron 1200 |

| Part Number | DHD1200AMT1B |

| Market | Desktop |

| Introduction | November 15, 2001 (announced) November 15, 2001 (launched) |

| Shop | Amazon |

| General Specs | |

| Family | Duron |

| Series | Duron Desktop |

| Locked | Yes |

| Frequency | 1200 MHz |

| Bus type | FSB |

| Bus speed | 100 MHz |

| Bus rate | 200 MT/s |

| Clock multiplier | 12 |

| CPUID | 670 |

| Microarchitecture | |

| Microarchitecture | K7 |

| Core Name | Morgan |

| Core Family | 6 |

| Core Model | 7 |

| Core Stepping | 0 |

| Process | 180 nm |

| Transistors | 25,180,000 |

| Technology | CMOS |

| Die | 105.68 mm² |

| Word Size | 32 bit |

| Cores | 1 |

| Threads | 1 |

| Max Memory | 4 GiB |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| Vcore | 1.75 V ± 0.15 V |

| TDP | 54.7 W |

| Tcase | 0 °C – 90 °C |

| Tstorage | -40 °C – 100 °C |

The Duron 1200 based on the Morgan core was a 32-bit x86 microprocessor developed by AMD and introduced in late 2001. This model was part of the second generation of the Duron family. Designed based on AMD's K7 (a Thunderbird-derivative) on a 180 nm process, this MPU operated at 1200 MHz with a bus capable of 200 MT/s with a max TDP of 54.7 W and a typical TDP of 50.3 W.

Cache[edit]

- Main article: K7 § Cache

| Cache Info [Edit Values] | ||

| L1I$ | 64 KiB 65,536 B 0.0625 MiB |

1x64 KiB 2-way set associative |

| L1D$ | 64 KiB 65,536 B 0.0625 MiB |

1x64 KiB 2-way set associative |

| L2$ | 64 KiB 0.0625 MiB 65,536 B 6.103516e-5 GiB |

1x64 KiB 16-way set associative |

Graphics[edit]

This SoC has no integrated graphics processing unit.

Features[edit]

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||

|

||||||||

- Halt State

- Sleep State

Documents[edit]

DataSheet[edit]

- AMD Duron Processor Model 7 Data Sheet; Publication # 24310; Rev: G; Issue Date: January 2002.

Other[edit]

- AMD Duron Processor Model 7 Revision Guide; Publication # 24806; Rev: E; Issue Date: October 2003.

Die Shot[edit]

See also[edit]

Facts about "Duron 1200 (Morgan) - AMD"

| base frequency | 1,200 MHz (1.2 GHz, 1,200,000 kHz) + |

| bus rate | 200 MT/s (0.2 GT/s, 200,000 kT/s) + |

| bus speed | 100 MHz (0.1 GHz, 100,000 kHz) + |

| bus type | FSB + |

| clock multiplier | 12 + |

| core count | 1 + |

| core family | 6 + |

| core model | 7 + |

| core name | Morgan + |

| core stepping | 0 + |

| core voltage | 1.75 V (17.5 dV, 175 cV, 1,750 mV) + |

| core voltage tolerance | 0.15 V + |

| cpuid | 670 + |

| designer | AMD + |

| die area | 105.68 mm² (0.164 in², 1.057 cm², 105,680,000 µm²) + |

| family | Duron + |

| first announced | November 15, 2001 + |

| first launched | November 15, 2001 + |

| full page name | amd/duron/dhd1200amt1b + |

| has feature | Halt State + and Sleep State + |

| has locked clock multiplier | true + |

| instance of | microprocessor + |

| l1d$ description | 2-way set associative + |

| l1d$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l1i$ description | 2-way set associative + |

| l1i$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l2$ description | 16-way set associative + |

| l2$ size | 0.0625 MiB (64 KiB, 65,536 B, 6.103516e-5 GiB) + |

| ldate | November 15, 2001 + |

| main image |  + + |

| manufacturer | AMD + |

| market segment | Desktop + |

| max case temperature | 363.15 K (90 °C, 194 °F, 653.67 °R) + |

| max cpu count | 1 + |

| max memory | 4,096 MiB (4,194,304 KiB, 4,294,967,296 B, 4 GiB, 0.00391 TiB) + |

| max storage temperature | 373.15 K (100 °C, 212 °F, 671.67 °R) + |

| microarchitecture | K7 + |

| min case temperature | 273.15 K (0 °C, 32 °F, 491.67 °R) + |

| min storage temperature | 233.15 K (-40 °C, -40 °F, 419.67 °R) + |

| model number | Duron 1200 + |

| name | Duron 1200 + |

| part number | DHD1200AMT1B + |

| process | 180 nm (0.18 μm, 1.8e-4 mm) + |

| series | Duron Desktop + |

| smp max ways | 1 + |

| tdp | 54.7 W (54,700 mW, 0.0734 hp, 0.0547 kW) + |

| technology | CMOS + |

| thread count | 1 + |

| transistor count | 25,180,000 + |

| word size | 32 bit (4 octets, 8 nibbles) + |