m (Bot: switching template from {{mpu}} to a more generic {{chip}}) |

|||

| (5 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

{{ambric title|Am2045}} | {{ambric title|Am2045}} | ||

| − | {{ | + | {{chip |

| name = Am2045 | | name = Am2045 | ||

| no image = | | no image = | ||

| Line 38: | Line 38: | ||

| die size = | | die size = | ||

| word size = 32 bit | | word size = 32 bit | ||

| − | | core count = | + | | core count = 344 |

| thread count = | | thread count = | ||

| max cpus = | | max cpus = | ||

| − | | max memory = 4 | + | | max memory = 4 GiB |

| electrical = | | electrical = | ||

| Line 73: | Line 73: | ||

| socket 0 type = BGA | | socket 0 type = BGA | ||

}} | }} | ||

| − | '''Am2045''' (later renamed '''Am2045A''') was [[Ambric]]'s original flagship [[MPPA]] introduced in late 2006. This model was made of {{ambric|am2000#Architecture| | + | '''Am2045''' (later renamed '''Am2045A'''), codename '''[[codename::Kestrel]]''', was [[Ambric]]'s original flagship [[MPPA]] introduced in late 2006. This model was made of {{ambric|am2000#Architecture|43 Brics}} arranged as a grid of about 5x9, making up a total of 344 {{arch|32}} [[RICS]]-like cores operating asynchronously at 1-333 MHz. This model was later replace with {{\\|Am2045B}}. |

| − | Originally this chip was supposed to have 45 Brics, hence the '2045' which was supposed to have 360 cores. However the final model only had 42 | + | Originally this chip was supposed to have 45 Brics, hence the '2045' which was supposed to have 360 cores. However the final model only had 43 bric for 344 cores instead. Earlier models might have had only 42 brics at one point for 336 cores. |

== Architecture == | == Architecture == | ||

{{main|ambric/am2000#Architecture|l1=Am2000 § Architecture}} | {{main|ambric/am2000#Architecture|l1=Am2000 § Architecture}} | ||

| − | The Am2045 is made of | + | The Am2045 is made of 43 homogeneous 'Brics' laid out in a 5 by 9 grid to form 344 cores and 344 RAM units. |

General layout: | General layout: | ||

| − | * | + | * 43x Brics |

** 2x Computer Unit (CU) | ** 2x Computer Unit (CU) | ||

*** 2x SRD {{arch|32}} CPU | *** 2x SRD {{arch|32}} CPU | ||

| Line 90: | Line 90: | ||

== Cache == | == Cache == | ||

| − | The Am2045 contains | + | The Am2045 contains 43 Brics, each with its own [[RAM]] Unit (RU) of 13 kB of SRAM for a total of 559 kB of SRAM. |

== Memory controller == | == Memory controller == | ||

| Line 101: | Line 101: | ||

| bandwidth schan = | | bandwidth schan = | ||

| bandwidth dchan = | | bandwidth dchan = | ||

| − | | max memory = 4 | + | | max memory = 4 GiB |

}} | }} | ||

| Line 109: | Line 109: | ||

* 128x [[has feature::GPIO]] @ 100 MHz | * 128x [[has feature::GPIO]] @ 100 MHz | ||

* [[has feature::serial flash]] | * [[has feature::serial flash]] | ||

| + | |||

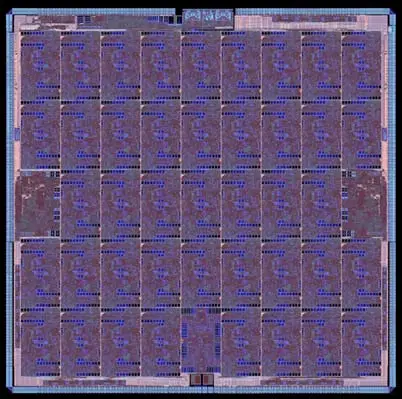

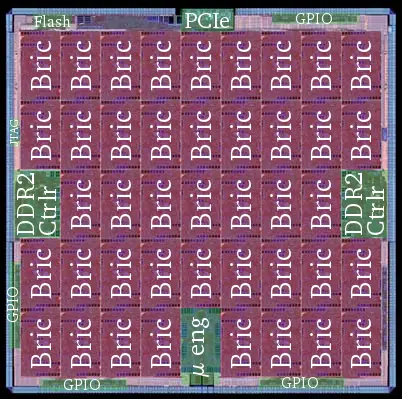

| + | == Die Shot == | ||

| + | {| | ||

| + | | [[File:Am2045 die shot.png]] || [[File:Am2045 die shot (annotated).png]] | ||

| + | |} | ||

Latest revision as of 15:16, 13 December 2017

| Edit Values | |

| Am2045 | |

| |

| Am2045 | |

| General Info | |

| Designer | Ambric |

| Model Number | Am2045 |

| Part Number | Am2045, Am2045A |

| Market | Embedded |

| Introduction | October 10, 2006 (announced) January 2007 (launched) |

| End-of-life | 2012 (last order) 2012 (last shipment) |

| General Specs | |

| Family | Am2000 |

| Series | Gen 1 |

| Locked | No |

| Frequency | 333 MHz |

| Bus speed | 100 MHz |

| Clock multiplier | 3.3 |

| Microarchitecture | |

| Microarchitecture | Ambric |

| Process | 130 nm |

| Transistors | 117,000,000 |

| Technology | CMOS |

| Word Size | 32 bit |

| Cores | 344 |

| Max Memory | 4 GiB |

Am2045 (later renamed Am2045A), codename Kestrel, was Ambric's original flagship MPPA introduced in late 2006. This model was made of 43 Brics arranged as a grid of about 5x9, making up a total of 344 32-bit RICS-like cores operating asynchronously at 1-333 MHz. This model was later replace with Am2045B.

Originally this chip was supposed to have 45 Brics, hence the '2045' which was supposed to have 360 cores. However the final model only had 43 bric for 344 cores instead. Earlier models might have had only 42 brics at one point for 336 cores.

Architecture[edit]

- Main article: Am2000 § Architecture

The Am2045 is made of 43 homogeneous 'Brics' laid out in a 5 by 9 grid to form 344 cores and 344 RAM units.

General layout:

- 43x Brics

Cache[edit]

The Am2045 contains 43 Brics, each with its own RAM Unit (RU) of 13 kB of SRAM for a total of 559 kB of SRAM.

Memory controller[edit]

| Integrated Memory Controller | |

| Type | DDR2-400 |

| Controllers | 2 |

| Channels | 1 |

| Max memory | 4 GiB |

Expansions[edit]

- PCIe

- JTAG

- 128x GPIO @ 100 MHz

- serial flash

Die Shot[edit]

|

|

| base frequency | 333 MHz (0.333 GHz, 333,000 kHz) + |

| bus speed | 100 MHz (0.1 GHz, 100,000 kHz) + |

| clock multiplier | 3.3 + |

| codename | Kestrel + |

| core count | 344 + |

| designer | Ambric + |

| family | Am2000 + |

| first announced | October 10, 2006 + |

| first launched | January 2007 + |

| full page name | ambric/am2000/am2045 + |

| has feature | PCIe +, JTAG +, GPIO + and serial flash + |

| has locked clock multiplier | false + |

| instance of | microprocessor + |

| last order | 2012 + |

| last shipment | 2012 + |

| ldate | January 2007 + |

| main image |  + + |

| main image caption | Am2045 + |

| market segment | Embedded + |

| max memory | 4,096 MiB (4,194,304 KiB, 4,294,967,296 B, 4 GiB, 0.00391 TiB) + |

| microarchitecture | Ambric + |

| model number | Am2045 + |

| name | Am2045 + |

| part number | Am2045 + and Am2045A + |

| process | 130 nm (0.13 μm, 1.3e-4 mm) + |

| series | Gen 1 + |

| technology | CMOS + |

| transistor count | 117,000,000 + |

| word size | 32 bit (4 octets, 8 nibbles) + |