(→Panel Architecture) |

|||

| Line 87: | Line 87: | ||

=== Panel Architecture === | === Panel Architecture === | ||

| − | + | [[File:xiaomi panel-based data affinity architecture.png|right|450px]] | |

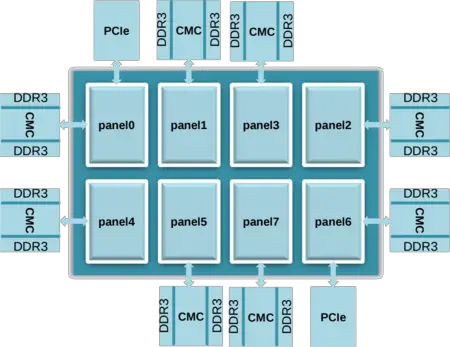

| + | Phytium organizes their processors using a grid-layout they call '''Panels''' they call '''Panel-based data affinity architecture'''. Each panel consists of 8 independent [[ARMv8]]-compatible cores. Phytium "Mars" processor consists of 8 such panels for a total of [[64 cores]]. Panels are interconnected with a 2-dimensional mesh network-on-a-chip [[level 2 cache]] with 4 MiB per panel for a total of 32 MiB. | ||

| + | |||

| + | In addition to the main die, Mars uses an additional '''Cache & Memory chips''' ('''CMC''') auxiliary chips. "Mars" uses 8 such chips connected to the main die providing 16 MiB of [[level 3 cache]] for a total of 128 MiB as well as 8 dual-channel DDR3-1600 [[memory controller]]s for a total maximum bandwidth of 204 GB/s. Mars also provides two 16-lane PCIe 3.0 interfaces. The chips incorporates ECC and parity protection on all caches, tags, and TLBs. | ||

=== Block Diagram === | === Block Diagram === | ||

Revision as of 23:47, 9 February 2017

| Edit Values | |

| Xiaomi µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Phytium |

| Manufacturer | TSMC |

| Introduction | 2017 |

| Process | 28 nm |

| Pipeline | |

| Type | Superscalar |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | ARMv8 |

| Cores | |

| Core Names | FTC660, FTC661 |

Xiaomi is an ARM microarchitecture designed in-house by Phytium for their consumer market and server-based microprocessors.

Contents

Brands

| Codename | Brand | Description |

|---|---|---|

| Mars | FT-2000 |

|

| Earth | FT-1500A |

|

Architecture

Overview

- Fully ARMv8 compatible

- Support AArch32 and AArch64 modes

- EL0-EL3 supported

- ASIMD-128

- 28 nm process

- Scalable design

- 4 to 64 cores

- Mesh topology network-on-chip

- Panel-based (grid) architecture

- Global cache coherency

- 2x DDR3-1600 channels per panel

- ECC support

- 2x 16-lane PCIe 3.0

Panel Architecture

Phytium organizes their processors using a grid-layout they call Panels they call Panel-based data affinity architecture. Each panel consists of 8 independent ARMv8-compatible cores. Phytium "Mars" processor consists of 8 such panels for a total of 64 cores. Panels are interconnected with a 2-dimensional mesh network-on-a-chip level 2 cache with 4 MiB per panel for a total of 32 MiB.

In addition to the main die, Mars uses an additional Cache & Memory chips (CMC) auxiliary chips. "Mars" uses 8 such chips connected to the main die providing 16 MiB of level 3 cache for a total of 128 MiB as well as 8 dual-channel DDR3-1600 memory controllers for a total maximum bandwidth of 204 GB/s. Mars also provides two 16-lane PCIe 3.0 interfaces. The chips incorporates ECC and parity protection on all caches, tags, and TLBs.

Block Diagram

| This section is empty; you can help add the missing info by editing this page. |

Memory Hierarchy

| This section is empty; you can help add the missing info by editing this page. |

Pipeline

| This section is empty; you can help add the missing info by editing this page. |

References

- Zhang, C. (2015, August). Mars: A 64-core ARMv8 processor. In Hot Chips 27 Symposium (HCS), 2015 IEEE (pp. 1-23). IEEE.

| codename | Xiaomi + |

| designer | Phytium + |

| first launched | 2017 + |

| full page name | phytium/microarchitectures/xiaomi + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Xiaomi + |

| process | 28 nm (0.028 μm, 2.8e-5 mm) + |