(→Brands) |

|||

| Line 63: | Line 63: | ||

| {{intel|Iris Pro Graphics 580}} || 72 || GT4e || {{intel|Skylake H|H|l=core}} || 128 MiB | | {{intel|Iris Pro Graphics 580}} || 72 || GT4e || {{intel|Skylake H|H|l=core}} || 128 MiB | ||

|} | |} | ||

| + | |||

| + | ==== Hardware Accelerated Video ==== | ||

| + | {{skylake hardware accelerated video table}} | ||

== Process Technology == | == Process Technology == | ||

Revision as of 22:28, 25 January 2017

| Edit Values | |

| Gen9 LP µarch | |

| General Info | |

| Arch Type | GPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | August 5, 2015 |

| Process | 14 nm |

| Succession | |

Gen9 LP (Generation 9 Low Power) is the microarchitecture for Intel's graphics processing unit utilized by Skylake-based microprocessors. Gen9 LP is the successor to Gen8 LP used by Broadwell. The Gen9 microarchitecture is designed separately by Intel and then integrated onto the same Skylake SoC die.

Contents

Codenames

Various models support different Graphics Tiers (GT) which provides different levels of performance. Some models also support an additional eDRAM side cache.

| Code Name | Description |

|---|---|

| GT1 | Contains 1 slice with 12 execution units. |

| GT2 | Contains 1 slice with 24 execution units. |

| GT3 | Contains 2 slices with 48 execution units. |

| GT3e | Contains 2 slices with 48 execution units. Has an additional eDRAM side cache. |

| Halo (GT4) | Contains 3 slices with 72 execution units. |

| Halo+e (GT4e) | Contains 3 slices with 72 execution units. Has an additional eDRAM side cache. |

Models

| Gen9 LP IGP Models | Standards | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Name | Execution Units | Tier | Series | eDRAM | Vulkan | Direct3D | OpenGL | OpenCL | |||||

| Windows | Linux | Windows | Linux | HLSL | Windows | Linux | Windows | Linux | |||||

| HD Graphics (Skylake) | 12 | GT1 | Y | - | 1.0 | 12 | N/A | 5.1 | 4.4 | 4.5 | 2.0 | ||

| HD Graphics 510 | 12 | GT1 | U, S | - | |||||||||

| HD Graphics 515 | 24 | GT2 | Y | - | |||||||||

| HD Graphics 520 | 24 | GT2 | U | - | |||||||||

| HD Graphics 530 | 24 | GT2 | H, S | - | |||||||||

| HD Graphics P530 | 24 | GT2 | H | - | |||||||||

| Iris Graphics 540 | 48 | GT3e | U | 64 MiB | |||||||||

| Iris Graphics 550 | 48 | GT3e | U | 64 MiB | |||||||||

| Iris Pro Graphics 580 | 72 | GT4e | H | 128 MiB | |||||||||

Hardware Accelerated Video

| [Edit] Skylake (Gen9) Hardware Accelerated Video Capabilities | |||||||

|---|---|---|---|---|---|---|---|

| Codec | Encode | Decode | |||||

| Profiles | Levels | Max Resolution | Profiles | Levels | Max Resolution | ||

| MPEG-2 (H.262) | Main | High | 1080p (FHD) | Main | Main, High | 1080p (FHD) | |

| MPEG-4 AVC (H.264) | High, Main | 5.1 | 2160p (4K) | Main, High, SHP, MHP | 5.1 | 2160p (4K) | |

| JPEG/MJPEG | Baseline | - | 16k x 16k | Baseline | Unified | 16k x 16k | |

| HEVC (H.265) | Main | 5.1 | 2160p (4K) | Main, Main 10 | 5.1 | 2160p (4K) | |

| VC-1 | ✘ | Advanced, Main, Simple | 3, High | 3840x3840 | |||

| VP8 | Unified | Unified | - | 0 | Unified | 1080p | |

| VP9 | ✘ | 0 | Unified | 2160p (4K) | |||

Process Technology

- Main article: Broadwell § Process Technology

Gen9 LP are part of the Skylake SoC die which uses the same 14 nm process used for the Broadwell microarchitecture.

Architecture

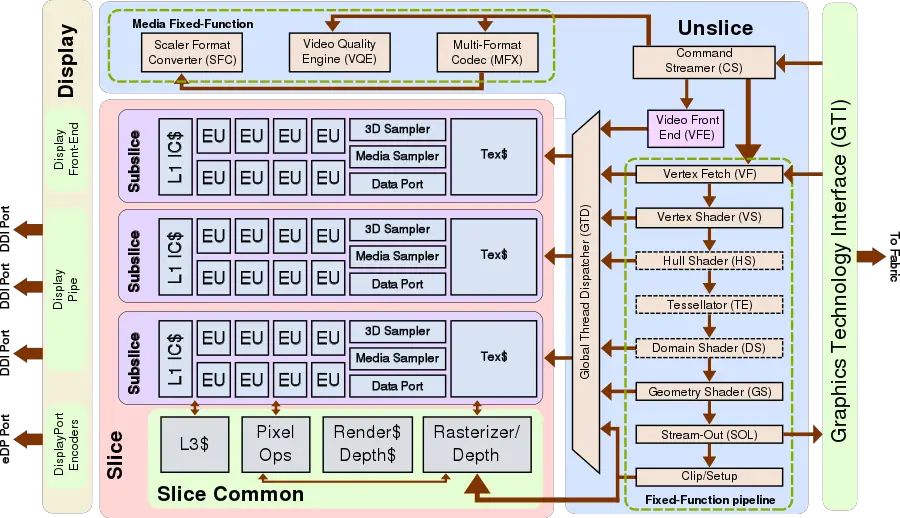

Gen9 LP presents a large departure from the Gen8 LP and previous architectures.

Key changes from Gen8 LP

- Architecture is drastically different

- Gen9 LP is composed of 3 truely independent major components: Display block, Unslice, and the Slice.

- Unslice

- Now sits on its own power gating/clock domain

- Capable of running at higher speeds if the situation allows (irrespective of slice clock)

- Can allow for pure fixed media alone

- Higher throughput

- Tessellator AutoStrip

- Fixed function video encoder in the Quick Sync engine

- codec (decode&encode) support for HEVC, VP8, MJPEG

- RAW imaging capabilities

- Now sits on its own power gating/clock domain

- Slice

- L3 Cache

- Increased to 768 KiB/slice (up from 576 KiB/slice)

- Request queue size was increased

- L3 Cache

- Subslice

- Adaptive scalable texture compression (ASTC)

- 16x multi-sample anti-aliasing (MSAA)

- Post depth test coverage mask

- Multi-plane overlays

- Texture samplers now natively support an NV12 YUV

- Preemption of execution is now supported at the thread level

- Round robin scheduling of threads within an execution unit.

- new native support for the 32-bit float atomics operations of min, max, and compare/exchange.

- 16-bit floating point capability is improved with native support for denormals and gradual underflow

- L4$

- The eDRAM is now a side cache instead of an L4$ like it was in Gen8 LP. (See Skylake §eDRAM architectural changes for the reason)

- Side-cache eDRAM was moved into the system agent adjacent to the display controller

Block Diagram

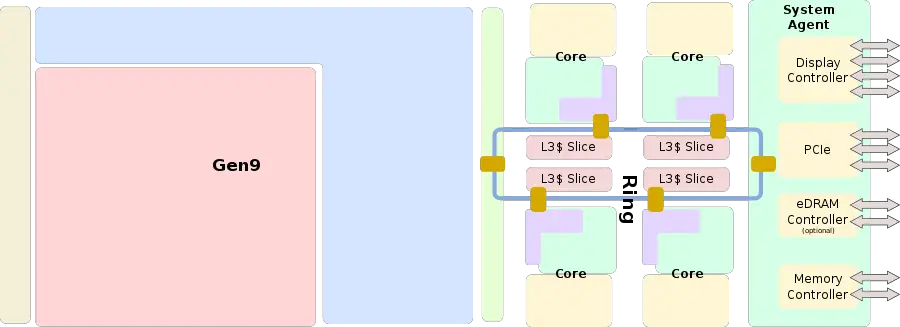

Entire SoC Overview

Gen9 LP

This block is for the most common setup, which is GT2 with 24 execution units.

Individual Core

Display

| This section is empty; you can help add the missing info by editing this page. |

Unslice

The Unslice is one of Gen9's major components and is responsible for the fixed-function geometry capabilities, fixed-function media capabilities, and it provides the interface to the memory fabric. One of the big changes in Gen9 is that the Unslice now sits on its own power/clock domain. This change allows the Unslice to operate at its own speed provided higher on-demand performance when desired. This change has a number of other benefits such as being able to turn off the slices (one or more) when they're not used in cases where pure fixed-function media is used. Additionally, the Unslice is now capable of running at a higher clock while the slice can run at a slower clock when the scenario demands it (such as in cases where higher fixed-function geometry or memory demands occur).

Slice

| This section is empty; you can help add the missing info by editing this page. |

| codename | Gen9 LP + |

| designer | Intel + |

| first launched | August 5, 2015 + |

| full page name | intel/microarchitectures/gen9 + |

| instance of | microarchitecture + |

| manufacturer | Intel + |

| microarchitecture type | GPU + |

| name | Gen9 LP + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |