From WikiChip

Difference between revisions of "intel/xeon e7"

| Line 42: | Line 42: | ||

== Members == | == Members == | ||

| − | === Westmere | + | === Westmere EX === |

{{main|intel/microarchitectures/westmere|l1=Westmere µarch}} | {{main|intel/microarchitectures/westmere|l1=Westmere µarch}} | ||

{{empty section}} | {{empty section}} | ||

| Line 52: | Line 52: | ||

* 10 cores | * 10 cores | ||

| − | === Ivy Bridge | + | === Ivy Bridge EX (v2) === |

{{main|intel/microarchitectures/ivy bridge|l1=Ivy Bridge µarch}} | {{main|intel/microarchitectures/ivy bridge|l1=Ivy Bridge µarch}} | ||

{{empty section}} | {{empty section}} | ||

| Line 62: | Line 62: | ||

* 15 cores | * 15 cores | ||

| − | === Haswell | + | === Haswell EX (v3) === |

{{main|intel/microarchitectures/haswell|l1=Haswell µarch}} | {{main|intel/microarchitectures/haswell|l1=Haswell µarch}} | ||

{{empty section}} | {{empty section}} | ||

| Line 72: | Line 72: | ||

* 18 cores | * 18 cores | ||

| − | === Broadwell | + | === Broadwell EX (v4) === |

{{main|intel/microarchitectures/broadwell|l1=Broadwell µarch}} | {{main|intel/microarchitectures/broadwell|l1=Broadwell µarch}} | ||

{{empty section}} | {{empty section}} | ||

Revision as of 19:34, 12 June 2016

| Intel Xeon E7 | |

| Developer | Intel |

| Manufacturer | Intel |

| Type | Microprocessors |

| Introduction | April 5, 2011 (announced) April 5, 2011 (launch) |

| Architecture | Multi-socket server microprocessors |

| ISA | x86-64 |

| µarch | Westmere, Ivy Bridge, Haswell, Broadwell |

| Word size | 64 bit 8 octets

16 nibbles |

| Process | 32 nm 0.032 μm , 22 nm3.2e-5 mm 0.022 μm , 14 nm2.2e-5 mm 0.014 μm

1.4e-5 mm |

| Technology | CMOS |

| Clock | 1700 MHz-3400 MHZ |

| Package | FCLGA-1567 |

| Socket | LGA-1567-1 |

Xeon E7 is a family of high-end enterprise-level x86 microprocessors. These server processors offer the highest performance, most extensive set of features, and offer multi-socket configuration support.

Contents

Members

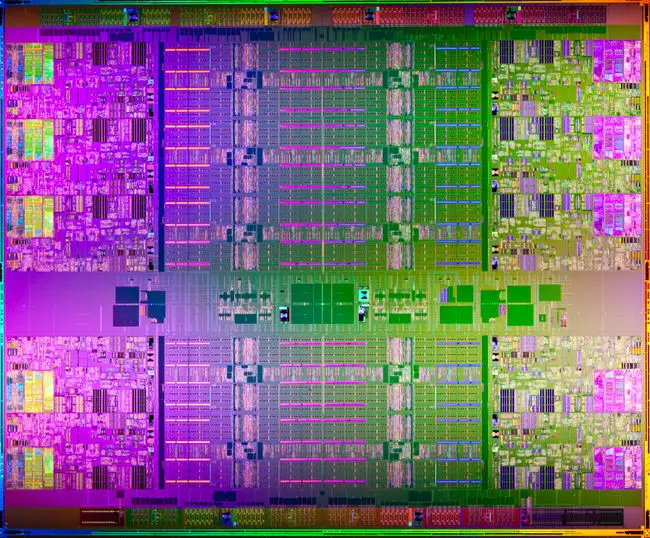

Westmere EX

- Main article: Westmere µarch

| This section is empty; you can help add the missing info by editing this page. |

Die Shot

- 513 mm²

- 2,600,000,000 transistors

- 10 cores

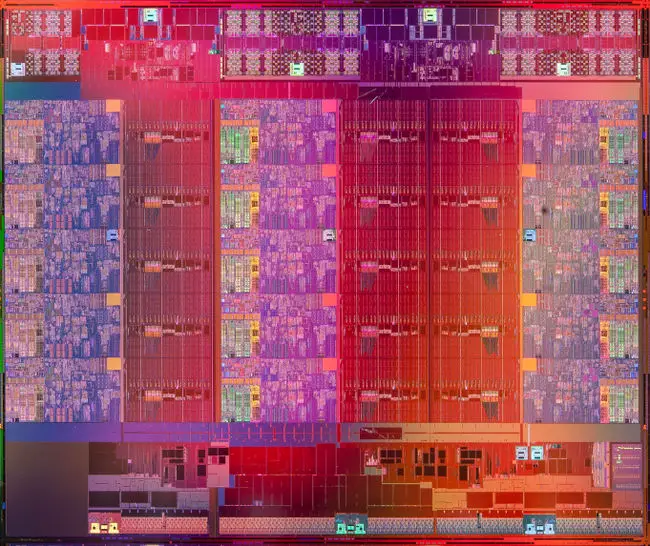

Ivy Bridge EX (v2)

- Main article: Ivy Bridge µarch

| This section is empty; you can help add the missing info by editing this page. |

Die Shot

- 541 mm²

- 4,310,000,000 transistors

- 15 cores

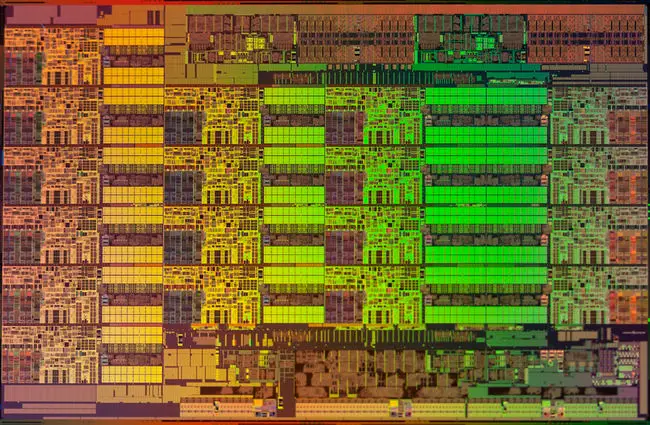

Haswell EX (v3)

- Main article: Haswell µarch

| This section is empty; you can help add the missing info by editing this page. |

Die Shot

- 662 mm²

- 5,690,000,000 transistors

- 18 cores

Broadwell EX (v4)

- Main article: Broadwell µarch

| This section is empty; you can help add the missing info by editing this page. |

See Also

Facts about "Xeon E7 - Intel"

| designer | Intel + |

| first announced | April 5, 2011 + |

| first launched | April 5, 2011 + |

| full page name | intel/xeon e7 + |

| instance of | microprocessor family + |

| instruction set architecture | x86-64 + |

| main designer | Intel + |

| manufacturer | Intel + |

| microarchitecture | Westmere +, Ivy Bridge +, Haswell + and Broadwell + |

| name | Intel Xeon E7 + |

| package | FCLGA-1567 + |

| process | 32 nm (0.032 μm, 3.2e-5 mm) +, 22 nm (0.022 μm, 2.2e-5 mm) + and 14 nm (0.014 μm, 1.4e-5 mm) + |

| socket | LGA-1567-1 + |

| technology | CMOS + |

| word size | 64 bit (8 octets, 16 nibbles) + |