From WikiChip

File list

This special page shows all uploaded files.

First page |

Previous page |

Next page |

Last page |

| Date | Name | Thumbnail | Size | Description | Versions |

|---|---|---|---|---|---|

| 17:43, 8 June 2017 | skylake-sp memory.svg (file) |  |

11 KB | Intel {{intel|Skylake|l=arch}}-SP New memory hierarchy. | 1 |

| 06:44, 23 June 2017 | PEZY Computing (March 7, 2017).pdf (file) |  |

2.21 MB | PEZY computing; {{pezy|PEZY-SC2}}, {{pezy|PEZY-SC3}}, {{pezy|PEZY-SC4}} | 1 |

| 17:03, 24 June 2017 | arm1 pipeline.svg (file) | 11 KB | slightly more detailed | 2 | |

| 18:36, 24 June 2017 | arm1 pc.svg (file) |  |

5 KB | The program counter of the {{armh|ARM1}} | 1 |

| 17:08, 2 July 2017 | core i9x logo.png (file) |  |

540 KB | Intel {{intel|Core i9}}X logo, Introduced May 30, 2017 | 1 |

| 18:12, 20 July 2017 | z14 core layout.png (file) |  |

551 KB | IBM {{ibm|z14|l=arch}} core layout. Image by IBM. | 1 |

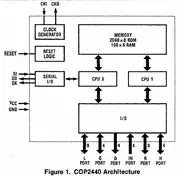

| 00:38, 22 July 2017 | original COP2440 block diagram.png (file) |  |

122 KB | National Semicondcutor {{national|COP2440}} original block diagram by National. | 1 |

| 00:21, 5 September 2017 | hisilicon logo.svg (file) | 99 KB | HiSilicon logo | 1 | |

| 00:30, 6 September 2017 | k3v1 prod brief.pdf (file) |  |

151 KB | HiSilicon {{hisilicon|K3V1}} Product Brief | 1 |

| 01:16, 6 September 2017 | hisilicon k3v1 block.png (file) | 341 KB | HiSilicon {{hisilicon|K3V1}} block diagram. | 1 | |

| 02:03, 6 September 2017 | hi3620.png (file) |  |

35 KB | HiSilicon {{hisil|Hi3620}} | 1 |

| 12:02, 6 September 2017 | hisilicon k3v2 block.png (file) | 54 KB | HiSilicon {{hisilicon|k3v2}} block diagram | 1 | |

| 21:03, 6 September 2017 | hisilicon kirin logo.svg (file) | 5 KB | HiSilicon {{hisil|Kirin}} logo | 1 | |

| 00:47, 7 September 2017 | kirin 970.png (file) |  |

1.76 MB | HiSilicon Kirin 970. Image by Huawei | 1 |

| 13:43, 7 September 2017 | kirin 970 npu.png (file) |  |

765 KB | NPU performance shown by Mr. Yu during 2017 IFA. Image from Huawei stream. | 1 |

| 15:48, 9 September 2017 | core-overview-of-2nd-generation-intel-core-processor-family-brief.pdf (file) |  |

1.28 MB | 2nd Generation Intel® Core Processor Family | 1 |

| 15:48, 9 September 2017 | performance-2nd-gen-core-product-brief.pdf (file) |  |

1.54 MB | 2nd Generation Intel® Core vPro Processor Family | 1 |

| 15:48, 9 September 2017 | performance-2nd-generation-core-vpro-family-paper.pdf (file) |  |

3.32 MB | 2nd Generation Intel® Core vPro Processor Family New levels of security, manageability, and responsiveness White Paper * 2nd Gen Intel® Core i7 vPro Processor * 2nd Gen Intel® Core i5 vPro Processor | 1 |

| 15:12, 10 September 2017 | helio p30.png (file) |  |

385 KB | 2 | |

| 15:12, 10 September 2017 | helio p23.png (file) |  |

385 KB | 2 | |

| 22:03, 12 September 2017 | a11 intro keynote event.png (file) |  |

803 KB | Apple {{apple|A11}} intro slide from Apple's Keynote Event September 2017. | 1 |

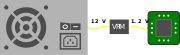

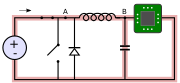

| 00:28, 15 October 2017 | vrm general.svg (file) |  |

19 KB | 2 | |

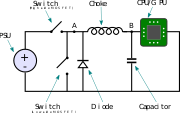

| 13:13, 15 October 2017 | vrm circut.svg (file) |  |

30 KB | changed a bit for our explination | 3 |

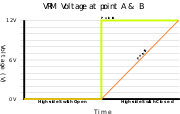

| 14:06, 15 October 2017 | vrm voltage at points a-b when high side switch is on-off.svg (file) |  |

12 KB | 2 | |

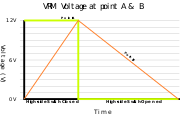

| 14:49, 15 October 2017 | vrm voltage at points a-b when high side switch is off-on.svg (file) |  |

12 KB | 2 | |

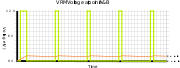

| 19:07, 15 October 2017 | vrm voltage 12v to 1p2v.svg (file) |  |

26 KB | 2 | |

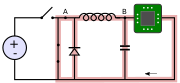

| 19:24, 15 October 2017 | vrm circut (high-side closed).svg (file) |  |

21 KB | VRM high-side closed. | 1 |

| 19:24, 15 October 2017 | vrm circut (high-side open).svg (file) |  |

22 KB | VRM high-side open. | 1 |

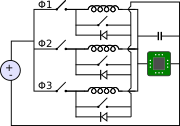

| 20:26, 15 October 2017 | vrm circut (multi-phase).svg (file) |  |

37 KB | Multi-phase VRM circuit | 1 |

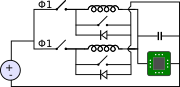

| 20:53, 15 October 2017 | vrm circut with switching (multi-phase).svg (file) |  |

31 KB | VRM switching with multi-phase. | 1 |

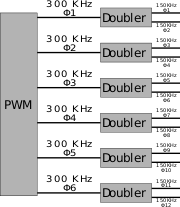

| 01:50, 16 October 2017 | pwd doubler 6 to 12 phase.svg (file) |  |

30 KB | VRM 6 phase PWD doubled to 12.. | 1 |

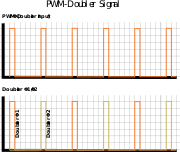

| 02:42, 16 October 2017 | pwm-doubler input output.svg (file) |  |

28 KB | PWD Phase Doubler input/output graph. | 1 |

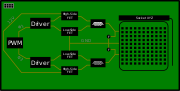

| 03:31, 16 October 2017 | vrm on board drawing.svg (file) |  |

58 KB | VRM on board drawing. | 1 |

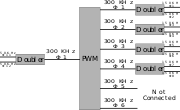

| 17:51, 16 October 2017 | vrm 6+1 into 8+1.svg (file) |  |

26 KB | VRM 6+1 real into 8 virtual + 1 | 1 |

| 00:16, 17 October 2017 | P6X58D Premium vrm.png (file) |  |

11.96 MB | VRM (MOSTFETs unexposted) on the P6X58D Premium motherboard. | 1 |

| 01:02, 17 October 2017 | P6X58D Premium vrm detailed.png (file) |  |

10.58 MB | P6X58D Premium VRM detailed. | 1 |

| 01:15, 17 October 2017 | P6X58D Premium back pem.png (file) |  |

4.18 MB | P6X58D Premium back PEM, VRM. | 1 |

| 13:21, 17 October 2017 | vrm circut with switching (multi-phase) output overlay.svg (file) |  |

32 KB | VRM switching with multi-phase with the output overlayed. | 1 |

| 20:10, 17 October 2017 | vrm power reg unit.svg (file) | 16 KB | slightly better | 2 | |

| 22:16, 17 October 2017 | vrm pwm analog.svg (file) |  |

16 KB | 2 | |

| 23:37, 17 October 2017 | vrm pwm analog wave.svg (file) | 20 KB | VRM PWM analog wave. | 1 | |

| 00:23, 18 October 2017 | vrm pwm digital.svg (file) |  |

13 KB | VRM PWM digital wave | 1 |

| 01:03, 18 October 2017 | vrm pwm digital wave.svg (file) | 15 KB | Wave of a the PWM of a digital VRM. | 1 | |

| 02:04, 18 October 2017 | ISL6366 pwm vrm example.png (file) |  |

464 KB | 3 | |

| 03:40, 18 October 2017 | vrm circut (2 channels 1 phase).svg (file) |  |

30 KB | VRM with two channels but a single phase. | 1 |

| 23:05, 18 October 2017 | current vs cpu load.svg (file) |  |

23 KB | Current vs CPU Load, in the context of Load-Line Calibration. | 1 |

| 08:48, 19 October 2017 | current vs cpu load and voltage.svg (file) |  |

30 KB | 2 | |

| 10:17, 19 October 2017 | current vs cpu load and voltage with dynamic change.svg (file) |  |

26 KB | VRM current vs cpu load and voltage with dynamic change | 1 |

| 16:57, 19 October 2017 | current vs cpu load and voltage with droop shown.svg (file) |  |

40 KB | VRM with current vs cpu load and voltage shown with voltage droop marked. | 1 |

| 22:15, 19 October 2017 | cpu load voltage and droop.svg (file) |  |

26 KB | 3 |

First page |

Previous page |

Next page |

Last page |