From WikiChip

Information for "renesas/r-car/e2"

Basic information

| Display title | R-Car E2 - Renesas |

| Default sort key | R-Car E2, Intel |

| Page length (in bytes) | 2,925 |

| Page ID | 21344 |

| Page content language | English (en) |

| Page content model | wikitext |

| Indexing by robots | Allowed |

| Number of redirects to this page | 7 |

| Counted as a content page | Yes |

| Number of subpages of this page | 0 (0 redirects; 0 non-redirects) |

Page protection

| Edit | Allow all users (infinite) |

| Move | Allow all users (infinite) |

Edit history

| Page creator | BCD (talk | contribs) |

| Date of page creation | 01:17, 22 July 2017 |

| Latest editor | ChippyBot (talk | contribs) |

| Date of latest edit | 15:32, 13 December 2017 |

| Total number of edits | 6 |

| Total number of distinct authors | 2 |

| Recent number of edits (within past 90 days) | 0 |

| Recent number of distinct authors | 0 |

Page properties

| Transcluded templates (18) | Templates used on this page:

|

Facts about "R-Car E2 - Renesas"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | R-Car E2 - Renesas#package + |

| base frequency | 1,000 MHz (1 GHz, 1,000,000 kHz) + and 780 MHz (0.78 GHz, 780,000 kHz) + |

| core count | 3 + |

| core name | Cortex-A7 + and SH-4A + |

| core voltage | 1 V (10 dV, 100 cV, 1,000 mV) + |

| designer | Renesas + and ARM Holdings + |

| family | R-Car + |

| first announced | October 22, 2014 + |

| first launched | June 2016 + |

| full page name | renesas/r-car/e2 + |

| has ecc memory support | false + |

| instance of | microprocessor + |

| integrated gpu | PowerVR SGX540 + |

| integrated gpu base frequency | 260 MHz (0.26 GHz, 260,000 KHz) + |

| integrated gpu designer | Imagination Technologies + |

| integrated gpu execution units | 1 + |

| io voltage | 3.3 V (33 dV, 330 cV, 3,300 mV) + and 1.8 V (18 dV, 180 cV, 1,800 mV) + |

| isa | ARMv7 + and SuperH + |

| isa family | ARM + and SuperH + |

| l1$ size | 192 KiB (196,608 B, 0.188 MiB) + |

| l1d$ size | 96 KiB (98,304 B, 0.0938 MiB) + |

| l1i$ size | 96 KiB (98,304 B, 0.0938 MiB) + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| ldate | June 2016 + |

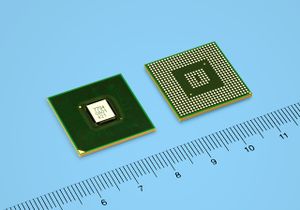

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Embedded + |

| max cpu count | 1 + |

| max memory | 2,048 MiB (2,097,152 KiB, 2,147,483,648 B, 2 GiB, 0.00195 TiB) + |

| max memory bandwidth | 9.93 GiB/s (10,168.32 MiB/s, 10.662 GB/s, 10,662.256 MB/s, 0.0097 TiB/s, 0.0107 TB/s) + |

| max memory channels | 2 + |

| microarchitecture | Cortex-A7 + and SH-4A + |

| model number | E2 + |

| name | R-Car E2 + |

| package | FCBGA-501 + |

| part number | R8A7794 + |

| process | 28 nm (0.028 μm, 2.8e-5 mm) + |

| series | 2nd Gen + |

| smp max ways | 1 + |

| supported memory type | DDR3-1333 + |

| technology | CMOS + |

| thread count | 3 + |

| word size | 32 bit (4 octets, 8 nibbles) + |