From WikiChip

Editing renesas/r-car/m2

Warning: You are editing an out-of-date revision of this page. If you save it, any changes made since this revision will be lost.

Warning: You are not logged in. Your IP address will be publicly visible if you make any edits. If you log in or create an account, your edits will be attributed to your username, along with other benefits.

This page supports semantic in-text annotations (e.g. "[[Is specified as::World Heritage Site]]") to build structured and queryable content provided by Semantic MediaWiki. For a comprehensive description on how to use annotations or the #ask parser function, please have a look at the getting started, in-text annotation, or inline queries help pages.

Facts about "R-Car M2 - Renesas"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | R-Car M2 - Renesas#package + |

| base frequency | 1,500 MHz (1.5 GHz, 1,500,000 kHz) + |

| core count | 3 + |

| core name | Cortex-A15 + and SH-4A + |

| core voltage | 1.03 V (10.3 dV, 103 cV, 1,030 mV) + |

| designer | Renesas + and ARM Holdings + |

| family | R-Car + |

| first announced | September 26, 2013 + |

| first launched | June 2015 + |

| full page name | renesas/r-car/m2 + |

| has ecc memory support | false + |

| instance of | microprocessor + |

| integrated gpu | PowerVR SGX544 + |

| integrated gpu base frequency | 520 MHz (0.52 GHz, 520,000 KHz) + |

| integrated gpu designer | Imagination Technologies + |

| integrated gpu execution units | 2 + |

| io voltage | 1.8 V (18 dV, 180 cV, 1,800 mV) + and 3.3 V (33 dV, 330 cV, 3,300 mV) + |

| isa | ARMv7 + and SuperH + |

| isa family | ARM + and SuperH + |

| l1$ size | 192 KiB (196,608 B, 0.188 MiB) + |

| l1d$ size | 96 KiB (98,304 B, 0.0938 MiB) + |

| l1i$ size | 96 KiB (98,304 B, 0.0938 MiB) + |

| l2$ size | 2 MiB (2,048 KiB, 2,097,152 B, 0.00195 GiB) + |

| ldate | June 2015 + |

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Embedded + |

| max cpu count | 1 + |

| max memory bandwidth | 11.92 GiB/s (12,206.08 MiB/s, 12.799 GB/s, 12,799.003 MB/s, 0.0116 TiB/s, 0.0128 TB/s) + |

| max memory channels | 2 + |

| microarchitecture | Cortex-A15 + and SH-4A + |

| model number | M2 + |

| name | R-Car M2 + |

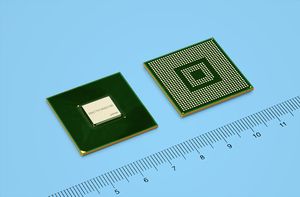

| package | FCBGA-831 + |

| part number | R8A7791 + |

| process | 28 nm (0.028 μm, 2.8e-5 mm) + |

| series | 2nd Gen + |

| smp max ways | 1 + |

| supported memory type | DDR3-1600 + |

| technology | CMOS + |

| thread count | 3 + |

| word size | 32 bit (4 octets, 8 nibbles) + |