From WikiChip

CN3630-400 SCP - Cavium

| Edit Values | |||||||

| Cavium CN3630-400 SCP | |||||||

| |||||||

| General Info | |||||||

| Designer | Cavium | ||||||

| Manufacturer | TSMC | ||||||

| Model Number | CN3630-400 SCP | ||||||

| Part Number | CN3630-400BG1521-SCP | ||||||

| Market | Networking | ||||||

| Introduction | August, 2005 (announced) August, 2005 (launched) | ||||||

| General Specs | |||||||

| Family | OCTEON | ||||||

| Series | CN3600 | ||||||

| Frequency | 400 MHz | ||||||

| Microarchitecture | |||||||

| ISA | MIPS64 (MIPS) | ||||||

| Microarchitecture | cnMIPS | ||||||

| Core Name | cnMIPS | ||||||

| Process | 130 nm | ||||||

| Technology | CMOS | ||||||

| Word Size | 64 bit | ||||||

| Cores | 4 | ||||||

| Threads | 4 | ||||||

| Max Memory | 16 GiB | ||||||

| Multiprocessing | |||||||

| Max SMP | 1-Way (Uniprocessor) | ||||||

| Electrical | |||||||

| Power dissipation | 14 W | ||||||

| Packaging | |||||||

| |||||||

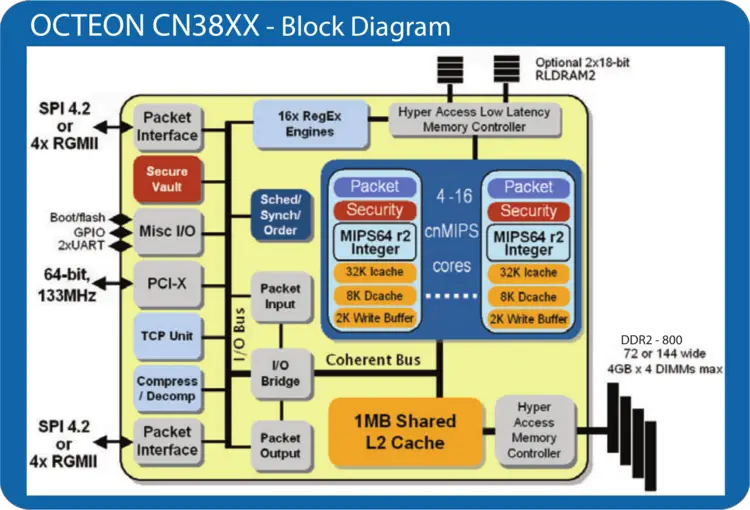

The CN3630-400 SCP is a 64-bit quad-core MIPS secure network communication microprocessor (SNP) designed by Cavium and introduced in 2005. This processor, which incorporates four cnMIPS cores, operates at 400 MHz and dissipates 14 Watts. This processor includes a number of hardware networking accelerators including units for high-performance packet I/O processing, QoS, TCP, and encryption. This MPU supports up to 16 GiB of DDR2-800 ECC memory.

Contents

Cache[edit]

- Main article: cnMIPS § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Expansions[edit]

|

Expansion Options

|

||||||||||||||||

|

||||||||||||||||

Networking[edit]

|

Networking

|

||||||||

|

||||||||

Hardware Accelerators[edit]

[Edit/Modify Accelerators Info]

|

Hardware Accelerators

|

||||||||||||

|

||||||||||||

Block diagram[edit]

Datasheet[edit]

Facts about "CN3630-400 SCP - Cavium"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | CN3630-400 SCP - Cavium#package + |

| base frequency | 400 MHz (0.4 GHz, 400,000 kHz) + |

| core count | 4 + |

| core name | cnMIPS + |

| designer | Cavium + |

| family | OCTEON + |

| first announced | August 2005 + |

| first launched | August 2005 + |

| full page name | cavium/octeon/cn3630-400bg1521-scp + |

| has ecc memory support | true + |

| has hardware accelerators for cryptography | true + |

| has hardware accelerators for network quality of service processing | true + |

| has hardware accelerators for tcp packet processing | true + |

| instance of | microprocessor + |

| isa | MIPS64 + |

| isa family | MIPS + |

| l1$ size | 160 KiB (163,840 B, 0.156 MiB) + |

| l1d$ description | 64-way set associative + |

| l1d$ size | 32 KiB (32,768 B, 0.0313 MiB) + |

| l1i$ description | 64-way set associative + |

| l1i$ size | 128 KiB (131,072 B, 0.125 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| ldate | August 2005 + |

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Networking + |

| max cpu count | 1 + |

| max memory | 16,384 MiB (16,777,216 KiB, 17,179,869,184 B, 16 GiB, 0.0156 TiB) + |

| max memory bandwidth | 5.96 GiB/s (6,103.04 MiB/s, 6.4 GB/s, 6,399.501 MB/s, 0.00582 TiB/s, 0.0064 TB/s) + |

| max memory channels | 1 + |

| microarchitecture | cnMIPS + |

| model number | CN3630-400 SCP + |

| name | Cavium CN3630-400 SCP + |

| package | FCBGA-1521 + |

| part number | CN3630-400BG1521-SCP + |

| power dissipation | 14 W (14,000 mW, 0.0188 hp, 0.014 kW) + |

| process | 130 nm (0.13 μm, 1.3e-4 mm) + |

| series | CN3600 + |

| smp max ways | 1 + |

| supported memory type | DDR2-800 + |

| technology | CMOS + |

| thread count | 4 + |

| word size | 64 bit (8 octets, 16 nibbles) + |