Instruction Set Architecture

- Instructions

- Addressing Modes

- Calling Convention

- Microarchitectures

- Model-Specific Register

- CPUID

- Assembly

- Interrupts

- Registers

- Micro-Ops

- Timer

Advanced Matrix Extension (AMX) is an x86 extension that introduces a matrix register file and new instructions for operating on matrices.

Contents

Overview[edit]

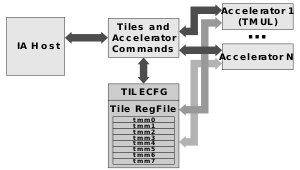

The Advanced Matrix Extension (AMX) is an x86 extension that introduces a new programming framework for working with matrices (rank-2 tensors). The extensions introduce two new components: a 2-dimensional register file with registers called 'tiles' and a set of accelerators that are able to operate on those tiles. The tiles represent a sub-array portion from a large 2-dimensional memory image. AMX instructions are synchronous in the instruction stream with memory load/store operations by tiles being coherent with the host's memory accesses. AMX instructions may be freely interleaved with traditional x86 code and execute in parallel with other extensions (e.g., AVX512) with special tile loads and stores and accelerator commands being sent over to the accelerator for execution.

Palettes[edit]

Determining the kind of operations available on specific hardware can be done by enumerating a palette of options.

Currently, 2 palettes exist:

- Palette 0 - initialized state

- Palette 1 - an 8-tile register file with each register being 16 rows x 64-byte (1 KiB) for a total register file of 8 KiB.

A programmer can configure the size of the register file by configuring tiles of smaller dimensions to suit their algorithm. Tiles may be configured in rows and bytes_per_row which are stored as metadata for the accelerator to operate on. Information pertaining to the palette is stored in a tile control register (TILECFG) and is accessible via the palette_table CPUID leaf 1DH. The TILECFG is programmed using the LDTILECFG instruction.

Accelerators[edit]

AMX supports a set of accelerators that can operate on tiles. Currently, just one accelerator is defined.

Tile matrix multiply unit (TMUL)[edit]

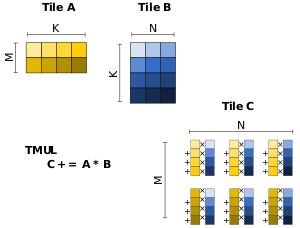

The Tile Matrix Multiply (TMUL) Unit is an accelerator as part of AMX comprising a grid of fused multiply-add units capable of operating on tiles. Its existence is defined by the AMX-INT8 and AMX-BF16 sub-extensions. The TMUL unit instruction set computes TileC[M][N] += TileA[M][K] * TileB[K][N].

The TMUL unit comes with a number of parameters supported including the maximum height (tmul_maxk) and maximum SIMD dimension (tmul_maxn). Those parameters are dynamically read by the TMUL unit upon execution.

Instructions[edit]

AMX introduces 12 new instructions:

Configuration:

-

LDTILECFG- Load tile configuration, loads the tile configuration from the 64-byte memory location specified. -

STTILECFG- Store tile configuration, stores the tile configuration in the 64-byte memory location specified.

Data:

-

TILELOADD/TILELOADDT1- Load tile -

TILESTORED- Store tile -

TILERELEASE- Release tile, returns TILECFG and TILEDATA to the INIT state -

TILEZERO- Zero tile, zeroes the destination tile

Operation:

-

TDPBF16PS- Perform a dot-product of BF16 tiles and accumulate the result. Packed Single Accumulation. -

TDPB[XX]D- Perform a dot-product of Int8 tiles and accumulate the result. Dword Accumulation.- Where XX can be: SU = Signed/Unsigned, US = Unsigned/Signed, SS = Signed/Signed, and UU = Unsigned/Unsigned pairs.

Feature set[edit]

Not all hardware implementations support all operations. The AMX extension comprises three sub-extensions: AMX-TILE, AMX-INT8, and AMX-BF16.

| Instruction | Feature Set | ||

|---|---|---|---|

| Base | TMUL | ||

| AMX-TILE | AMX-INT8 | AMX-BF16 | |

LDTILECFG |

✔ | ||

STTILECFG |

✔ | ||

TILELOADDTILELOADDT1 |

✔ | ||

TILESTORED |

✔ | ||

TILERELEASE |

✔ | ||

TILEZERO |

✔ | ||

TDPBSSD

|

✔ | ||

TDPBF16PS |

✔ | ||

Detection[edit]

| CPUID | Instruction Set | |

|---|---|---|

| Input | Output | |

| EAX=07H, ECX=0 | EDX[bit 22] | AMX-BF16 |

| EDX[bit 24] | AMX-TILE | |

| EDX[bit 25] | AMX-INT8 | |

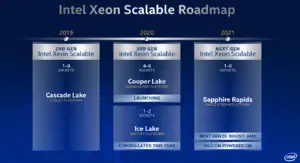

Microarchitecture support[edit]

| Microarchitecture | AMX-TILE | AMX-INT8 | AMX-BF16 |

|---|---|---|---|

| Sapphire Rapids | ✔ | ✔ | ✔ |

Intrinsic functions[edit]

Bibliography[edit]

- Intel Architecture Instruction Set Extensions and Future Features Programming Reference, Revision 40. (Ref #319433-040)