-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

Chip-on-Wafer-on-Substrate (CoWoS)

< tsmc

| v · d · e | |

| Packaging | |

| |

| Technologies | |

| Concepts | |

| Single-Row | |

| Dual-Row | |

| Quad-Row | |

| Grid Array | |

| 2.5D IC | |

| 3D IC | |

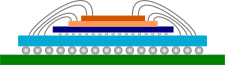

Chip-on-Wafer-on-Substrate (CoWoS) is a two-point-five dimensional integrated circuit (2.5D IC) through-silicon via (TSV) interposer-based packaging technology designed by TSMC.

Overview

CoWoS is a wafer-level multi-chip packaging technology that incorporates multiple chiplets side-by-side on a silicon interposer in order to achieve better interconnect density and performance. The chiplets are bonded through micro-bumps on a silicon interposer forming a chip-on-wafer (CoW). The CoW is then subsequently thinned such that the TSV perforations are exposed. This is followed C4 bumps formation and singulation. A CoWoS package is completed thrugh bonding to a package substrate.

Retrieved from "https://en.wikichip.org/w/index.php?title=tsmc/cowos&oldid=86004"