m (→Self-Aligned Contacts (SAC)) |

(→Boosters) |

||

| Line 25: | Line 25: | ||

{{main|contact over active gate|l1=Contact Over Active Gate (COAG)}} | {{main|contact over active gate|l1=Contact Over Active Gate (COAG)}} | ||

Typically, the area between the end of the nMOS and pMOS devices is used as the gate contact hit location. In an effort to reduce cell height, engineering effort was placed on reducing that region. '''Self-aligned Contact Over Active Gate''' ('''COAG''') is a process enhancement technique that eliminates the need to land the contact outside of the active gate, allowing the gate contact to land directly over the active gate, thereby reducing the amount of space the end-to-end (ETE) spacing between devices. | Typically, the area between the end of the nMOS and pMOS devices is used as the gate contact hit location. In an effort to reduce cell height, engineering effort was placed on reducing that region. '''Self-aligned Contact Over Active Gate''' ('''COAG''') is a process enhancement technique that eliminates the need to land the contact outside of the active gate, allowing the gate contact to land directly over the active gate, thereby reducing the amount of space the end-to-end (ETE) spacing between devices. | ||

| + | |||

| + | :[[File:scaling with coag.svg|400px]] | ||

=== Buried Power Rail (BPR) === | === Buried Power Rail (BPR) === | ||

Revision as of 23:42, 19 June 2022

A scaling booster is an enhancement made to a process node beyond classical scaling vectors in order to allow Moore's Law device scaling to continue or accelerate.

Contents

Overview

As process nodes continues to shrink, classical scaling vectors (e.g., gate pitch) becomes increasingly challenging. There are multiple reasons for this including electrostatics in the FEOL, RC delays in the BEOL, as well as general routing challenges. Scaling boosters have been introduced in order to aid traditional scaling vectors through various modifications and enhancements. Scaling boosters may be part of the process technology flow itself or as part of the standard library as part of the design-technology co-optimization (DTCO). By combining scaling boosters with slightly less aggressive classical scaling vectors, a process node can achieve similar transistors density while keeping the process cost in check.

Boosters

Track Reduction

- Main article: Track Reduction

Track Reduction (also called Fin Depopulation in the context of FinFET) is a technique for improving the density of the standard cell library by reducing the number of fins per FinFET transistor or the height of the active N or P region. By reducing the height of the active region, the number of tracks is reduced thereby reducing the height of the standard cell and ultimately increasing the transistor density of the chip. In the case of FinFET, fin depopulation results in energy reduction but also performance reduction.

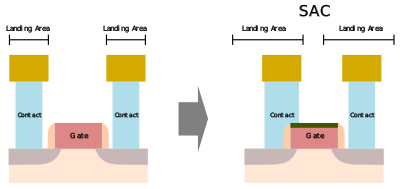

Self-Aligned Contacts (SAC)

- Main article: self-aligned contact (SAC)

As nodes continued to shrink the various features, the landing area for the gate contacts shrunk to a point where decreasing the pitch any further would result in uneconomical yield loss. Self-aligned contact (SAC) is a process enhancement technique that loosens up the alignment tolerances associated with the landing area of the gate contacts, thereby allowing the contacted gate pitch to shrink further while improving the yield by preventing yield loss due to the contact shorting the gate.

Self-Aligned Vias (SAV)

| This section is empty; you can help add the missing info by editing this page. |

Single Diffusion Break (SDB)

| This section is empty; you can help add the missing info by editing this page. |

Mixed Diffusion Break (MDB)

| This section is empty; you can help add the missing info by editing this page. |

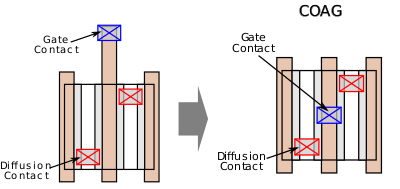

Contact Over Active Gate (COAG)

- Main article: Contact Over Active Gate (COAG)

Typically, the area between the end of the nMOS and pMOS devices is used as the gate contact hit location. In an effort to reduce cell height, engineering effort was placed on reducing that region. Self-aligned Contact Over Active Gate (COAG) is a process enhancement technique that eliminates the need to land the contact outside of the active gate, allowing the gate contact to land directly over the active gate, thereby reducing the amount of space the end-to-end (ETE) spacing between devices.

Buried Power Rail (BPR)

| This section is empty; you can help add the missing info by editing this page. |

SuperVia

SuperVia is the concept of having a Via etch through 2 metal dielectrics stack instead of landing on the bottom metal to and have another via on the bottom metal. This helps with routing concerns and improves scaling.

Fully Self Aligned Via (FSAV)

| This section is empty; you can help add the missing info by editing this page. |

Self-Aligned Block (SAB)

| This section is empty; you can help add the missing info by editing this page. |