From WikiChip

Process-Architecture-Optimization (PAO) - Intel

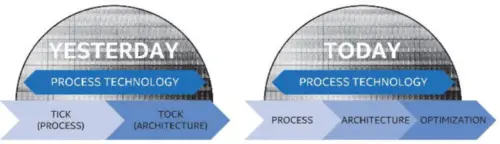

Process-Architecture-Optimization is a development model introduced by Intel for their mainstream microprocessors in 2016 following the phase-out of their Tick-Tock model. The change is a result of the increase in cost and complexity of advancing lithography processes in the past decade. Under the new model the amount of time utilized for any given process technology is lengthened as Moore's Law increases in complexity with smaller nodes.

Under the Process-Architecture-Optimization Model:

- Process - With each process, Intel advances their manufacturing process technology in line with Moore's Law. Each new process introduces higher transistor density and a generally a plethora of other advantages such as higher performance and lower power consumption. During a "process", Intel retrofits their previous microarchitecture to the new process which inherently yields better performance and energy saving. During a "process", usually just a few features and improvements are introduced.

- Architecture - With each architecture, Intel uses the their latest manufacturing process technology from their "process" to manufacture a newly designed microarchitecture. The new microarchitecture is designed with the new process in mind and typically introduces Intel's newest big features and functionalities. New instructions are often added during this cycle stage.

- Optimization - With each optimization, Intel improves upon their previous microarchitecture by introducing incremental improvements and enhancements without introducing any large charges. Additionally the process itself enjoys various refinements as it matures. (For example with Kaby Lake, an optimized process called "14 nm+" is used. The enhanced process had a number of transistor-level modifications done to it (e.g. taller fins) allowing for higher frequency at identical voltage levels.)

Roadmap

| Intel PAO Roadmap | |||

|---|---|---|---|

| Cycle | Process | Introduction | Microarchitecture |

| Process | 14 nm | 2014 | Broadwell |

| Architecture | 14 nm | 2015 | Skylake (Client) |

| Optimization | 14 nm+ | 2016 | Kaby Lake |

| Optimization | 14 nm++ | 2017 | Coffee Lake / Skylake (Server) |

| Optimization | 14 nm++ | 2018 | Whiskey Lake |

| Optimization | 14 nm++ | 2018 | Cascade Lake |

| Optimization | 14 nm++ | 2019 | Cooper Lake |

| Process | 10 nm | 2018 | Cannon Lake |

| Architecture | 10 nm+ | 2019 | Ice Lake |

| Optimization | 10 nm+ | 2020 | Tiger Lake |

| Optimization | 10 nm++ | 2021 | Alder Lake |

| Optimization | 10 nm++ | 2021 | Sapphire Rapids |

| Process | 7 nm | 2022 | Granite Rapids |

| Process | 7 nm | 2022 | Meteor Lake |

Facts about "Process-Architecture-Optimization (PAO) - Intel"

| instance of | development model + |

| name | Process-Architecture-Optimization + |