From WikiChip

Editing intel/cores/kaby lake s

Warning: You are not logged in. Your IP address will be publicly visible if you make any edits. If you log in or create an account, your edits will be attributed to your username, along with other benefits.

The edit can be undone.

Please check the comparison below to verify that this is what you want to do, and then save the changes below to finish undoing the edit.

This page supports semantic in-text annotations (e.g. "[[Is specified as::World Heritage Site]]") to build structured and queryable content provided by Semantic MediaWiki. For a comprehensive description on how to use annotations or the #ask parser function, please have a look at the getting started, in-text annotation, or inline queries help pages.

| Latest revision | Your text | ||

| Line 1: | Line 1: | ||

{{intel title|Kaby Lake S|core}} | {{intel title|Kaby Lake S|core}} | ||

{{core | {{core | ||

| − | |name=Kaby Lake S | + | | name = Kaby Lake S |

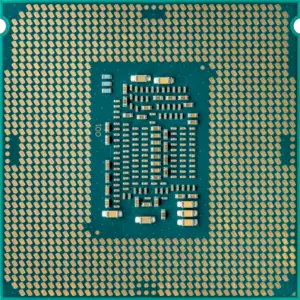

| − | |image=kaby lake s (front).png | + | | image = kaby lake s (front).png |

| − | |image 2=kaby lake s (back).png | + | | image size = 250px |

| − | |developer=Intel | + | | image 2 = kaby lake s (back).png |

| − | |manufacturer=Intel | + | | image 2 size = 250px |

| − | |first announced=January 3, 2017 | + | | developer = Intel |

| − | |first launched=January 3, 2017 | + | | manufacturer = Intel |

| − | |isa=x86-64 | + | | first announced = January 3, 2017 |

| − | + | | first launched = January 3, 2017 | |

| − | |microarch=Kaby Lake | + | | isa = x86-64 |

| − | |word=64 bit | + | | microarch = Kaby Lake |

| − | |proc=14 nm | + | | word = 64 bit |

| − | |tech=CMOS | + | | proc = 14 nm |

| − | |clock min=2,400 MHz | + | | tech = CMOS |

| − | |clock max=4,200 MHz | + | | clock min = 2,400 MHz |

| − | |predecessor=Skylake S | + | | clock max = 4,200 MHz |

| − | |predecessor link=intel/cores/skylake s | + | | package = FCLGA-1151 |

| − | |successor= | + | | socket = LGA-1151 |

| − | |successor link=intel/cores/ | + | |

| − | + | | succession = Yes | |

| − | + | | predecessor = Skylake S | |

| − | + | | predecessor link = intel/cores/skylake s | |

| + | | successor = Cannonlake S | ||

| + | | successor link = intel/cores/cannonlake s | ||

}} | }} | ||

'''Kaby Lake S''' ('''KBL-S''') is the name of the core for [[Intel]]'s mainstream performance line of processors based on the {{intel|Kaby Lake|l=arch}} microarchitecture serving as a successor to {{intel|Skylake S|l=core}} core. These chips are primarily targeted towards desktop performance to value computers, AiOs, and minis. Kaby Lake S processors are fabricated on Intel's enhanced [[14 nm lithography process|14nm+ process]] and provide {{intel|kaby_lake#Key_changes_from_Skylake|slight enhancements over|l=arch}} comparable Skylake models. | '''Kaby Lake S''' ('''KBL-S''') is the name of the core for [[Intel]]'s mainstream performance line of processors based on the {{intel|Kaby Lake|l=arch}} microarchitecture serving as a successor to {{intel|Skylake S|l=core}} core. These chips are primarily targeted towards desktop performance to value computers, AiOs, and minis. Kaby Lake S processors are fabricated on Intel's enhanced [[14 nm lithography process|14nm+ process]] and provide {{intel|kaby_lake#Key_changes_from_Skylake|slight enhancements over|l=arch}} comparable Skylake models. | ||

| Line 39: | Line 41: | ||

* Everything up to SSE4.2 (SMM, FPU, NX, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, AES) (not all S models support {{x86|AVX2}}) | * Everything up to SSE4.2 (SMM, FPU, NX, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, AES) (not all S models support {{x86|AVX2}}) | ||

* Graphics | * Graphics | ||

| − | ** {{intel|HD Graphics 610}} ( | + | ** {{intel|HD Graphics 610}} (Gen 9.5 LP GT1) or {{intel|HD Graphics 630}} (Gen 9.5 LP GT2) |

** Base frequency of 350 MHz | ** Base frequency of 350 MHz | ||

** Burst frequency of 1-1.15 GHz | ** Burst frequency of 1-1.15 GHz | ||

| Line 73: | Line 75: | ||

|?integrated gpu base frequency | |?integrated gpu base frequency | ||

|?integrated gpu max frequency | |?integrated gpu max frequency | ||

| − | |?has intel turbo boost technology | + | |?has intel turbo boost technology 2.0 |

|?has simultaneous multithreading | |?has simultaneous multithreading | ||

|?has advanced vector extensions 2 | |?has advanced vector extensions 2 | ||

| Line 87: | Line 89: | ||

|userparam=22:16 | |userparam=22:16 | ||

|mainlabel=- | |mainlabel=- | ||

| − | |||

|limit=100 | |limit=100 | ||

}} | }} | ||

| Line 96: | Line 97: | ||

== See also == | == See also == | ||

[[File:kaby lake s (angle).png|right|thumb]] | [[File:kaby lake s (angle).png|right|thumb]] | ||

| − | {{intel | + | * {{intel|Kaby Lake|l=arch}} |

| − | * {{intel| | + | ** {{intel|Kaby Lake Y|l=core}} |

| − | ** {{intel|Skylake S|l=core}} | + | ** {{intel|Kaby Lake U|l=core}} |

| + | ** {{intel|Kaby Lake H|l=core}} | ||

| + | * {{intel|Skylake S|l=core}} | ||

| + | * {{intel|Goldmont|l=arch}} | ||

Facts about "Kaby Lake S - Cores - Intel"

| designer | Intel + |

| first announced | January 3, 2017 + |

| first launched | January 3, 2017 + |

| instance of | core + |

| isa | x86-64 + |

| isa family | x86 + |

| main image |  + and + and  + + |

| manufacturer | Intel + |

| microarchitecture | Kaby Lake + |

| name | Kaby Lake S + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| technology | CMOS + |

| word size | 64 bit (8 octets, 16 nibbles) + |