From WikiChip

Editing intel/cores/ice lake y

Warning: You are not logged in. Your IP address will be publicly visible if you make any edits. If you log in or create an account, your edits will be attributed to your username, along with other benefits.

The edit can be undone.

Please check the comparison below to verify that this is what you want to do, and then save the changes below to finish undoing the edit.

This page supports semantic in-text annotations (e.g. "[[Is specified as::World Heritage Site]]") to build structured and queryable content provided by Semantic MediaWiki. For a comprehensive description on how to use annotations or the #ask parser function, please have a look at the getting started, in-text annotation, or inline queries help pages.

| Latest revision | Your text | ||

| Line 2: | Line 2: | ||

{{core | {{core | ||

|name=Ice Lake Y | |name=Ice Lake Y | ||

| − | |image= | + | |no image=Yes |

| − | |||

| − | |||

|developer=Intel | |developer=Intel | ||

|manufacturer=Intel | |manufacturer=Intel | ||

| − | |||

| − | |||

|isa=x86-64 | |isa=x86-64 | ||

|microarch=Ice Lake | |microarch=Ice Lake | ||

| Line 14: | Line 10: | ||

|proc=10 nm | |proc=10 nm | ||

|tech=CMOS | |tech=CMOS | ||

| − | |package name 1=intel, | + | |package name 1=intel,bga_1377 |

|predecessor=Amber Lake Y | |predecessor=Amber Lake Y | ||

|predecessor link=intel/cores/amber lake y | |predecessor link=intel/cores/amber lake y | ||

| − | |successor= | + | |successor=Ice Lake Y |

| − | |successor link=intel/cores/ | + | |successor link=intel/cores/ice lake y |

}} | }} | ||

| − | '''Ice Lake Y''' ('''ICL-Y''') is | + | '''Ice Lake Y''' ('''ICL-Y''') is the name of the core for [[Intel]]'s extremly-low power line of processors based on the {{intel|Ice Lake|l=arch}} microarchitecture serving as a successor to the {{intel|Cannon Lake Y|l=core}} core. These chips are primarily targeted towards 2-in-1s detachable, tablets, and computer sticks. Cannon Lake Y processors are fabricated on Intel's enhanced [[10 nm process|10nm+ process]] and come at slightly higher clock frequencies. |

| + | |||

| + | |||

| + | {{future information}} | ||

== Overview == | == Overview == | ||

| − | + | {{empty section}} | |

=== Common Features === | === Common Features === | ||

| − | + | {{empty section}} | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

{{clear}} | {{clear}} | ||

== Ice Lake Y Processors == | == Ice Lake Y Processors == | ||

| + | {{future information}} | ||

| + | |||

<!-- NOTE: | <!-- NOTE: | ||

This table is generated automatically from the data in the actual articles. | This table is generated automatically from the data in the actual articles. | ||

| Line 55: | Line 40: | ||

--> | --> | ||

{{comp table start}} | {{comp table start}} | ||

| − | <table class="comptable sortable | + | <table class="comptable sortable tc5 tc6"> |

| − | {{comp table header|main| | + | {{comp table header|main|12:List of Ice Lake Y Processors}} |

| − | {{comp table header|main| | + | {{comp table header|main|9:Main processor|3:Integrated Graphics}} |

| − | {{comp table header|cols|Launched|Family|Cores|Threads|L3$|%TDP|%Frequency|%Turbo|Name|%Frequency|%Turbo}} | + | {{comp table header|cols|Price|Launched|Family|Cores|Threads|L3$|%TDP|%Frequency|%Turbo|Name|%Frequency|%Turbo}} |

{{#ask: [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[core name::Ice Lake Y]] | {{#ask: [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[core name::Ice Lake Y]] | ||

|?full page name | |?full page name | ||

|?model number | |?model number | ||

| + | |?release price | ||

|?first launched | |?first launched | ||

|?microprocessor family | |?microprocessor family | ||

| Line 68: | Line 54: | ||

|?l3$ size | |?l3$ size | ||

|?tdp | |?tdp | ||

| − | |?base frequency# | + | |?base frequency#GHz |

|?turbo frequency (1 core)#GHz | |?turbo frequency (1 core)#GHz | ||

|?integrated gpu | |?integrated gpu | ||

| Line 75: | Line 61: | ||

|format=template | |format=template | ||

|template=proc table 3 | |template=proc table 3 | ||

| − | |userparam= | + | |userparam=14 |

|mainlabel=- | |mainlabel=- | ||

}} | }} | ||

| Line 81: | Line 67: | ||

</table> | </table> | ||

{{comp table end}} | {{comp table end}} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

== See also == | == See also == | ||

{{intel ice lake core see also}} | {{intel ice lake core see also}} | ||

Facts about "Ice Lake Y - Cores - Intel"

| back image |  + + |

| designer | Intel + |

| first announced | December 2018 + |

| first launched | May 27, 2019 + |

| instance of | core + |

| isa | x86-64 + |

| main image |  + + |

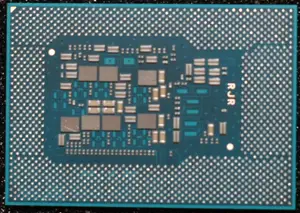

| main image caption | Ice Lake Y, front package + |

| manufacturer | Intel + |

| microarchitecture | Ice Lake + |

| name | Ice Lake Y + |

| package | FCBGA-1377 + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |

| socket | Type 3 + |

| technology | CMOS + |

| word size | 64 bit (8 octets, 16 nibbles) + |