| (One intermediate revision by the same user not shown) | |||

| Line 1: | Line 1: | ||

{{intel title|Integrated Connectivity (CNVi)}} | {{intel title|Integrated Connectivity (CNVi)}} | ||

| − | '''Integrated Connectivity''' ('''CNVi''') is an architecture for wireless connectivity devices designed by [[Intel]] for their processors. CNVi was introduced in [[2017]] with the launch of {{intel|Gemini Lake|l=core}} is planned for future mobile chipsets starting with {{intel|Cannon Lake|l=arch}}. | + | '''Integrated Connectivity''' ('''CNVi''') is an architecture for wireless connectivity devices designed by [[Intel]] for their processors. CNVi was introduced in [[2017]] with the launch of {{intel|Gemini Lake|l=core}} and is also planned for future mobile chipsets starting with {{intel|Cannon Lake|l=arch}}. |

== Overview == | == Overview == | ||

| Line 8: | Line 8: | ||

:[[File:intel cnvi architecture.png|800px]] | :[[File:intel cnvi architecture.png|800px]] | ||

| + | |||

| + | [[category:intel]] | ||

Latest revision as of 00:07, 27 December 2017

Integrated Connectivity (CNVi) is an architecture for wireless connectivity devices designed by Intel for their processors. CNVi was introduced in 2017 with the launch of Gemini Lake and is also planned for future mobile chipsets starting with Cannon Lake.

Overview[edit]

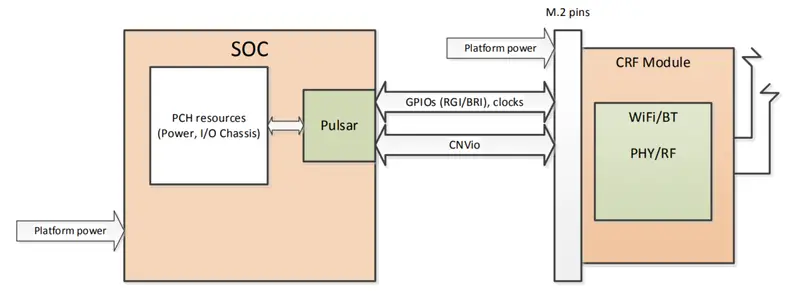

CNVi is an architecture for wireless connectivity designed by Intel for their recent mobile devices. Under the CNVi architecture, the large (and typically expensive) functional blocks found on a typical radio chip are moved onto the processor or chipset itself. This includes the processor and associated logic, memory, and the MAC components of the Bluetooth and Wi-Fi cores. The remaining parts (i.e., signal processor, analog and RF functions) are left on the Companion RF (CRF) module. This ultimately reduces the bill of material size and cost of the product.

The connectivity functionality that was moved to the SoC is incorporated in a block called a Pulsar. Pulsar interfaces with the rest of SoC through its internal interfaces and buses. Pulsar interfaces with the CRF module via the CNVio interface.