From WikiChip

Editing amd/cores/naples

Warning: You are not logged in. Your IP address will be publicly visible if you make any edits. If you log in or create an account, your edits will be attributed to your username, along with other benefits.

The edit can be undone.

Please check the comparison below to verify that this is what you want to do, and then save the changes below to finish undoing the edit.

This page supports semantic in-text annotations (e.g. "[[Is specified as::World Heritage Site]]") to build structured and queryable content provided by Semantic MediaWiki. For a comprehensive description on how to use annotations or the #ask parser function, please have a look at the getting started, in-text annotation, or inline queries help pages.

| Latest revision | Your text | ||

| Line 3: | Line 3: | ||

|name=Naples | |name=Naples | ||

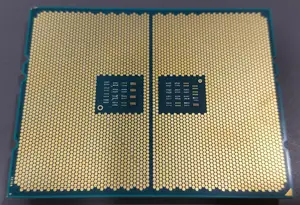

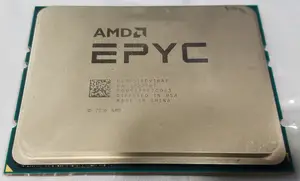

|image=amd naples (front).png | |image=amd naples (front).png | ||

| − | |caption= | + | |caption=Back |

|back image=amd naples (back).png | |back image=amd naples (back).png | ||

| + | |caption=Back | ||

|developer=AMD | |developer=AMD | ||

|manufacturer=GlobalFoundries | |manufacturer=GlobalFoundries | ||

| Line 24: | Line 25: | ||

== Overview == | == Overview == | ||

[[File:amd naples 2 sock.jpg|right|thumb]] | [[File:amd naples 2 sock.jpg|right|thumb]] | ||

| − | AMD Naples [[system on chips]] are a series of high-performance [[multiprocessors]] designed by [[AMD]] based on their {{amd|Zen|l=arch}} microarchitecture. Naples SoCs support both single and 2-way multiprocessing with up to a maximum of 32 cores (and 64 threads) per processor for a total of up to 64 cores (and 128 threads) for a 2-way MP system. Those SoCs sports 128 PCIe lanes each, however, half of them are lost when in 2-way MP (leaving the system with the same overall lanes count as a single socket solution). Communication between the two chips is done via AMD's {{amd|Infinity Fabric}} protocol over the 64 reserved lanes | + | AMD Naples [[system on chips]] are a series of high-performance [[multiprocessors]] designed by [[AMD]] based on their {{amd|Zen|l=arch}} microarchitecture. Naples SoCs support both single and 2-way multiprocessing with up to a maximum of 32 cores (and 64 threads) per processor for a total of up to 64 cores (and 128 threads) for a 2-way MP system. Those SoCs sports 128 PCIe lanes each, however, half of them are lost when in 2-way MP (leaving the system with the same overall lanes count as a single socket solution). Communication between the two chips is done via AMD's {{amd|Infinity Fabric}} protocol over the 64 reserved lanes. |

=== Common Features === | === Common Features === | ||

Facts about "Naples - Cores - AMD"

| back image |  + + |

| designer | AMD + |

| first announced | March 7, 2017 + |

| first launched | June 20, 2017 + |

| instance of | core + |

| isa | x86-64 + |

| main image |  + + |

| main image caption | Package, front + |

| manufacturer | GlobalFoundries + |

| microarchitecture | Zen + |

| name | Naples + |

| package | FCLGA-4094 + and SP3 + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| socket | LGA-4094 + and SP3 + |

| technology | CMOS + |

| word size | 64 bit (8 octets, 16 nibbles) + |