| Builder | |

| Developer | MathStar |

| Manufacturer | TSMC |

| Type | Programmable logic device |

| Introduction | 2002 (announced) 2003 (launch) |

| Production | 2003-2003 |

| Word size | 16 bit 2 octets

4 nibbles |

| Process | 130 nm 0.13 μm

1.3e-4 mm |

| Technology | CMOS |

| Clock | 100 MHz-1,000 MHz |

Builder was a family of FPOAs introduced by MathStar in 2003. This family the earliest attempt at designing an FPOA and was discontinued shortly after due to some technical issues.

Architecture

- Main article: field-programmable object array

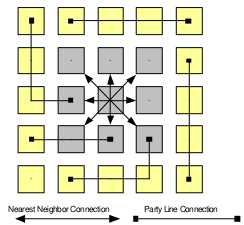

The Builder family was the MathStar's initial attempt at a field-programmable object array. Each chip contains 100s of silicon objects laid out in a grid, broken down to arrays of five objects each. Instructions are loaded to each of the objects at power-up.

Inter-Object communication was done primarily by passing data to the nearest neighbor through a unidirectional synchronous interconnect. Communication is configured dynamically and on-demand. Each object had the facilities needed for clock synchronization, built-in self-test, etc...

Object

There are five different types of components: Arithmetic Logic Unit (ALU), Content Addressable Memory (CAM), Cyclic Redundancy Check (CRC), Multiply Accumulator (MAC), and Register File (RF). The control program guides the overall program execution and the datapath setup. Datapath is 16-bit-bit but may be combined with adjacent objects to form larger datapaths of desired size.

| designer | MathStar + |

| first announced | 2002 + |

| first launched | 2003 + |

| full page name | mathstar/builder + |

| instance of | integrated circuit family + |

| main designer | MathStar + |

| manufacturer | TSMC + |

| name | Builder + |

| process | 130 nm (0.13 μm, 1.3e-4 mm) + |

| technology | CMOS + |

| word size | 16 bit (2 octets, 4 nibbles) + |