CMOS (Complementary metal–oxide–semiconductor) is a technique for constructing analog and digital logic circuits from two complementary MOS transistors - pMOS and nMOS. CMOS is the dominant technology used for VLSI and ULSI circuit chips used for anywhere from SRAM to microcontrollers and microprocessors.

Contents

Overview

- Main article: CMOS Complementary Topology

CMOS primarily makes use of what would otherwise be two separate circuit technologies - pMOS and nMOS. To better understand this, consider an nMOS transistor. Because it can pull no higher than VDD - Vt we get a degraded 1 output. Likewise with pMOS, we can pull no lower than Vt - a degraded 0 output. By combining both types, we can borrow the desired characteristics from both transistors such as a strong 0 and a strong 1.

CMOS circuits are designed with that concept in mind - always consisting of two separate sub-circuits called a PUN (pull-up network) and a PDN (pull-down network). CMOS logic must therefore by in one of two defined stages:

- PUN is open; PDN is conducting

- PUN is conducting; PDN is open

Conceptually they can be thought of as two switches, one controlling the connection between the output and VDD and one controlling the connection between the output and GND. Therefore it's important to note that if both switches are closed or both switches are open, the output will be ambiguous. The concept of a complementary topology ensures this does not happen. It should be noted that as the voltage on the transistor's gate changes, for a very brief moment both switches will be closed thereby creating a momentary spike in power consumption. This does become a problem with high frequency CMOS.

Inverter Example

- Main article: inverter

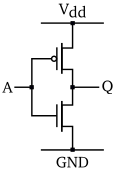

The simplest gate that can be implemented is the NOT gate which simply inverts the input. We can implement an inverter using a single nMOS and pMOS transistors. The pMOS transistor is connected to VDD while the nMOS transistor is connected to GND. When A is 0, the nMOS transistor turns OFF and the pMOS transistor turns ON. This results in Q being pulled up to 1 since the pMOS transistor will conduct VDD. Conversely, when A is 1, the nMOS transistor turns ON and the pMOS transistor turns OFF, thereby pulling Q down to GND.

Logic Families/Types

The use of static CMOS circuits with the standard PUN and PDN networks are used in the vast majority of combinational logic in integrated circuits. They are fast, low power, and have good noise margins. Perhaps the primary reason the majority of circuits are designed using static CMOS is simply due to the fact that its universally supported by CAD tools and in most standard cell libraries. Sometimes, however, specialized applications might have constraints that exceed what static CMOS can provide, for example power or area restrictions. For those occasions, various other CMOS logic families have been devised, each with their own advantages and disadvantages. Some of the common ones are listed below.

Static CMOS

- Main article: Static CMOS

Also called Full CMOS logic, static CMOS is the most commonly used logic style. Static logic provides high noise immunity, low static power consumption, and has relatively high test coverage. It does pose a number of weaknesses such as high fan-out load, and somewhat high noise generation.

Pseudo-NMOS Logic

- Main article: Pseudo-NMOS Logic

Pseudo-NMOS Logic circuit simply uses a pMOS transistor to satisfy CMOS's complementary topology. This type of logic allow high speed and low transistor count. However because of this very design, the output will experience reduced voltage swings and is thus susceptible to noise. When used sparingly, this circuit can provide substantial performance benefits at a cost of a small increase in static-power consumption. Additionally, when not used, the pMOS transistor can be used turned off shutting down the circuit at no additional cost.

Dynamic CMOS

- Main article: Dynamic CMOS

Dynamic CMOS uses a clocked pMOS PUN. This type of circuit has two phases: precharge and evaluation. When the clock is LOW, the output node is precharged to VDD (note that no current flows because the nMOS transistor is off). Once the clock goes back to HIGH the evaluation phase kicks in and the output will depend on the evaluation of the logic function implemented. Because inputs are hooked up to the nMOS transistors, the load capacitance is also smaller. This also makes it faster than static CMOS. Despite having almost half the number of transistors, this type of circuit still consumes more power than static CMOS due to the constant need to precharge and discharge of the output even if the input does not change. A side effect of this is that dynamic gates that are connected to the same clock signal cannot be directly cascaded since the monotonically falling output is not a suitable input to a second dynamic gate expecting monotonically rising signals.

Domino Logic

- Main articles: Domino Logic and Multiple-Output Domino Logic (MODL)

Domino logic solves the monotonicity problem in dynamic gates by placing a static CMOS inverter between cascading dynamic gates. The use of the inverter converts the monotonically falling output node into a rising one which is suitable for the next gate. The name domino gate is given to this dynamic-static CMOS pair because of its resemblance the behavior of domino tiles - all the gates are precharged simultaneously whereas the evaluation phase occurs sequentially.

Dual-rail Domino Logic

- Main article: Dual-rail Domino Logic

| This section is empty; you can help add the missing info by editing this page. |

NP Domino (Zipper)

- Main article: NP Domino

| This section is empty; you can help add the missing info by editing this page. |

Pass-Transistor Logic

- Main article: Pass-Transistor Logic

In Pass-Transistor Logic (PTL), inputs drive both gate terminals and source/drain terminals. In specialized circumstances, PTL can be significantly improve the speed, power, and area of the logic. In general, PTL usually yields equivalent logic to static CMOS - especially those making heavy use of transmission gates. PTL is not regenerative degrading the output as you chain them.

Complementary Pass-Transistor Logic

- Main article: Complementary Pass-Transistor Logic

Complementary Pass-Transistor Logic (CPTL) is a more specialized version of Pass-Transistor Logic which makes use of both the inputs and their complements. Likewise both the output and its complement gets generated.

Lean Integration with Pass Transistors

- Main article: Lean Integration with Pass Transistors

| This section is empty; you can help add the missing info by editing this page. |

Cascade Voltage Switch Logic

- Main article: Cascade Voltage Switch Logic (CVSL)

| This section is empty; you can help add the missing info by editing this page. |

| This article is still a stub and needs your attention. You can help improve this article by editing this page and adding the missing information. |