CMOS (Complementary metal–oxide–semiconductor) is a technique for constructing digital logic circuits from two complementary MOS transistors - pMOS and nMOS. CMOS is the dominant technology used for VLSI and ULSI circuit chips used for anywhere from SRAM to microcontrollers and microprocessors.

Overview

- Main article: CMOS Complementary Topology

CMOS primarily makes use of what would otherwise be two separate circuit technologies - pMOS and nMOS. To better understand this, consider an nMOS transistor. Because it can pull no higher than VDD - Vt we get a degraded 1 output. Likewise with pMOS, we can pull no lower than Vt - a degraded 0 output. By combining both types, we can borrow the desired characteristics from both transistors such as a strong 0 and a strong 1.

CMOS circuits are designed with that concept in mind - always consisting of two separate sub-circuits called a PUN (pull-up network) and a PDN (pull-down network). CMOS logic must therefore by in one of two defined stages:

- PUN is open; PDN is conducting

- PUN is conducting; PDN is open

Conceptually they can be thought of as two switches, one controlling the connection between the output and VDD and one controlling the connection between the output and GND. Therefore it's important to note that if both switches are closed or both switches are open, the output will be ambiguous. The concept of a complementary topology ensures this does not happen. It should be noted that as the voltage on the transistor's gate changes, for a very brief moment both switches will be closed thereby creating a momentary spike in power consumption. This does become a problem with high frequency CMOS.

Inverter Example

- Main article: inverter

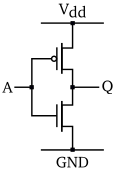

The simplest gate that can be implemented is the NOT gate which simply inverts the input. We can implement an inverter using a single nMOS and pMOS transistors. The pMOS transistor is connected to VDD while the nMOS transistor is connected to GND. When A is 0, the nMOS transistor turns OFF and the pMOS transistor turns ON. This results in Q being pulled up to 1 since the pMOS transistor will conduct VDD. Conversely, when A is 1, the nMOS transistor turns ON and the pMOS transistor turns OFF, thereby pulling Q down to GND.

| This article is still a stub and needs your attention. You can help improve this article by editing this page and adding the missing information. |