From WikiChip

File list

This special page shows all uploaded files.

First page |

Previous page |

Next page |

Last page |

| Date | Name | Thumbnail | Size | User | Description | Versions |

|---|---|---|---|---|---|---|

| 01:35, 2 October 2022 | i9-12900k (front).jpg (file) |  |

393 KB | David | Intel Alder Lake Core i9-12900K. Image by Intel. | 1 |

| 01:13, 2 October 2022 | pat gelsinger announces worlds first 6ghz processor.jpg (file) |  |

2.5 MB | David | Intel CEO Patrick Gelsinger announces the world's first 6 GHz processor based on the Raptor Lake. | 1 |

| 00:59, 2 October 2022 | intel raptor lake die (8+16).jpg (file) |  |

2.89 MB | David | Intel Raptor Lake SoC die shot. | 1 |

| 02:03, 9 July 2022 | sunny cove block diagram.svg (file) |  |

162 KB | David | 6 | |

| 23:58, 5 July 2022 | skylake server block diagram.svg (file) |  |

140 KB | David | 6 | |

| 23:01, 5 July 2022 | skylake block diagram.svg (file) |  |

136 KB | David | fixed decoder | 17 |

| 23:44, 20 June 2022 | iedm-2017-intel-10-sdg-tem.png (file) |  |

109 KB | David | Intel 10nm single dummy gate. | 1 |

| 23:44, 20 June 2022 | iedm-2017-intel-10-dummy-gates-tem.png (file) |  |

120 KB | David | Intel 10nm single dummy gate. | 1 |

| 23:41, 20 June 2022 | ddb-sdb-cell-changes.svg (file) |  |

35 KB | David | Single Diffusion Break -> Double Diffusion Break changes | 1 |

| 23:23, 20 June 2022 | ttt-cell-scaling-sdb.svg (file) |  |

42 KB | David | single dummy gate scaling booster | 1 |

| 22:41, 19 June 2022 | scaling with coag.svg (file) |  |

24 KB | David | Cell scaling with self-aligned contact over active gate. | 1 |

| 22:23, 19 June 2022 | iedm-2017-intel-10-wire-hs.png (file) |  |

234 KB | David | Intel 10nm COAG scaling benefits. | 1 |

| 22:05, 19 June 2022 | coag-diff.svg (file) |  |

22 KB | David | COAG | 1 |

| 21:42, 19 June 2022 | iedm-2017-intel-10-self-aligned-diffusion.png (file) |  |

196 KB | David | Intel 10nm self-aligned diffusion. IEDM 2017. | 1 |

| 21:42, 19 June 2022 | iedm-2017-intel-10-self-aligned-diffusion-marked.png (file) |  |

235 KB | David | Intel 10nm self-aligned diffusion. Marked. IEDM 2017. | 1 |

| 21:37, 19 June 2022 | iedm-2017-intel-10-self-aligned-gate-marked.png (file) |  |

111 KB | David | Intel 10-nanometer self-aligned gate. Marked. | 1 |

| 21:37, 19 June 2022 | iedm-2017-intel-10-self-aligned-gate.png (file) |  |

87 KB | David | Intel 10-nanometer self-aligned gate. | 1 |

| 14:47, 23 April 2022 | Socket G34 pinmap.svg (file) |  |

335 KB | QuietRub | 1 | |

| 16:06, 20 April 2022 | OPGA-453.svg (file) |  |

3 KB | QuietRub | 1 | |

| 16:05, 20 April 2022 | OPGA-940 AM3.svg (file) |  |

2 KB | QuietRub | 1 | |

| 16:03, 20 April 2022 | OPGA-941.svg (file) |  |

3 KB | QuietRub | 1 | |

| 16:03, 20 April 2022 | OPGA-938.svg (file) |  |

3 KB | QuietRub | 1 | |

| 16:02, 20 April 2022 | OPGA-940 AM2.svg (file) |  |

3 KB | QuietRub | 1 | |

| 16:01, 20 April 2022 | OPGA-563.svg (file) |  |

1 KB | QuietRub | 1 | |

| 15:59, 20 April 2022 | LGA-6096.svg (file) |  |

3 KB | QuietRub | 1 | |

| 15:58, 20 April 2022 | LGA-1718.svg (file) |  |

2 KB | QuietRub | 1 | |

| 15:57, 20 April 2022 | FCLGA-4094.svg (file) |  |

4 KB | QuietRub | Fixed pad distance E1. | 2 |

| 15:49, 20 April 2022 | OPGA-1331 pinmap.svg (file) |  |

239 KB | QuietRub | Flip/rotate version. | 2 |

| 18:59, 18 April 2022 | Socket AM5 PCB layout.svg (file) |  |

37 KB | QuietRub | 1 | |

| 18:58, 18 April 2022 | Socket AM5 backplate diag.svg (file) |  |

19 KB | QuietRub | 1 | |

| 18:57, 18 April 2022 | Socket AM5 housing diag.svg (file) |  |

33 KB | QuietRub | 1 | |

| 18:15, 18 April 2022 | Socket SP5 pinmap.svg (file) |  |

1,007 KB | QuietRub | 1 | |

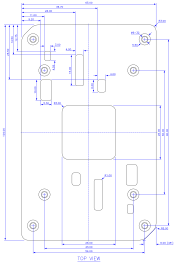

| 18:10, 18 April 2022 | Socket SP5 PCB layout.svg (file) |  |

33 KB | QuietRub | 1 | |

| 18:07, 18 April 2022 | Socket SP5 housing bv.svg (file) |  |

19 KB | QuietRub | 1 | |

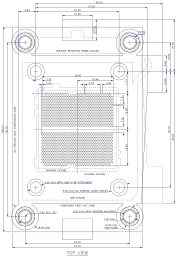

| 18:06, 18 April 2022 | Socket SP5 housing tv.svg (file) |  |

37 KB | QuietRub | 1 | |

| 18:01, 18 April 2022 | LGA-6096 carrier diag bv.svg (file) |  |

18 KB | QuietRub | 1 | |

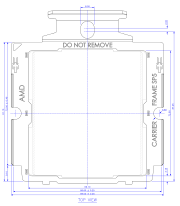

| 18:00, 18 April 2022 | LGA-6096 carrier diag tv.svg (file) |  |

21 KB | QuietRub | 1 | |

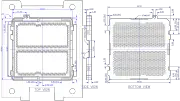

| 17:58, 18 April 2022 | LGA-6096 diag bv.svg (file) |  |

28 KB | QuietRub | 1 | |

| 17:57, 18 April 2022 | LGA-6096 diag tv.svg (file) |  |

17 KB | QuietRub | 1 | |

| 17:56, 18 April 2022 | Socket SP5 2P routing.svg (file) |  |

2 KB | QuietRub | 1 | |

| 14:37, 17 April 2022 | Socket TR4 pinmap.svg (file) |  |

655 KB | QuietRub | Corrections: DA18/DB18: GPP_CLK10P/N→GFX_CLK00P/N. Reference: AMD-55814-1.03. | 2 |

| 14:34, 17 April 2022 | LGA-4094 SP3r2 diag.svg (file) |  |

49 KB | QuietRub | 1 | |

| 14:33, 17 April 2022 | Socket TR4 routing.svg (file) |  |

6 KB | QuietRub | 1 | |

| 14:08, 17 April 2022 | Socket SP3 FIT housing diag.svg (file) |  |

51 KB | QuietRub | 1 | |

| 14:06, 17 April 2022 | Socket SP3 housing diag.svg (file) |  |

60 KB | QuietRub | 1 | |

| 16:43, 16 April 2022 | Socket SP3 Type-0 routing.svg (file) |  |

7 KB | QuietRub | 2 | |

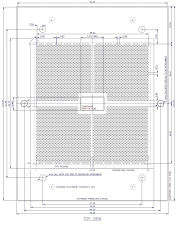

| 16:30, 16 April 2022 | Socket SP3 PCB layout.svg (file) |  |

34 KB | QuietRub | 1 | |

| 16:28, 16 April 2022 | LGA-4094 carrier diag.svg (file) |  |

32 KB | QuietRub | 1 | |

| 16:27, 16 April 2022 | LGA-4094 SP3 Rome diag.svg (file) |  |

18 KB | QuietRub | 1 | |

| 16:26, 16 April 2022 | LGA-4094 SP3 Naples diag.svg (file) |  |

20 KB | QuietRub | 1 |

First page |

Previous page |

Next page |

Last page |