From WikiChip

File list

This special page shows all uploaded files.

First page |

Previous page |

Next page |

Last page |

| Date | Name | Thumbnail | Size | Description | Versions |

|---|---|---|---|---|---|

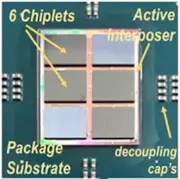

| 04:32, 29 February 2020 | tsarlet packaging photo.jpg (file) |  |

135 KB | CEA Leti {{cealeti|TSARLET|l=arch}} packaging photo. | 1 |

| 04:19, 29 February 2020 | tsarlet package.png (file) |  |

624 KB | CEA Leti {{cealeti|TSARLET|l=arch}} package. | 1 |

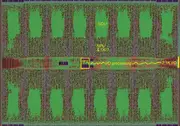

| 04:19, 29 February 2020 | tsarlet base interposer.png (file) |  |

2.02 MB | CEA Leti {{cealeti|TSARLET|l=arch}} base interposer die. | 1 |

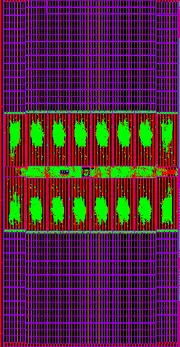

| 04:19, 29 February 2020 | tsarlet compute chiplet 2.png (file) |  |

1.11 MB | CEA Leti {{cealeti|TSARLET|l=arch}} compute chiplet. | 1 |

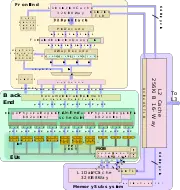

| 03:41, 29 February 2020 | tsarlet compute chiplet (annotated).png (file) |  |

802 KB | CEA Leti {{cealeti|TSARLET|l=arch}} chiplet die, annotated by WikiChip. | 1 |

| 03:21, 29 February 2020 | tsarlet compute chiplet.png (file) |  |

917 KB | CEA Leti {{cealeti|TSARLET|l=arch}} chiplet die. | 1 |

| 20:42, 28 February 2020 | cea-leti logo.jpg (file) |  |

34 KB | CEA-Leti logo. | 1 |

| 21:59, 21 February 2020 | ncore block diagram.svg (file) |  |

40 KB | 4 | |

| 19:45, 21 February 2020 | cha soc ncore die (logic).png (file) |  |

1.96 MB | Centaur Technology {{centtech|CHA|CHA NCORE|l=arch}} die logic portion. Photo by Centaur. | 1 |

| 18:46, 21 February 2020 | cha ncore.svg (file) |  |

15 KB | 4 | |

| 22:50, 16 February 2020 | helium vector reg file alias.svg (file) |  |

37 KB | Arm {{arm|Helium}} vector register file. | 1 |

| 19:44, 16 February 2020 | cortex-m55 tcm xbar.svg (file) |  |

30 KB | Arm {{armh|Cortex-M55|l=arch}} TCM xbar diagram by WikiChip. | 1 |

| 18:39, 16 February 2020 | cortex-m55 general block.png (file) |  |

102 KB | Arm {{armh|Cortex-M55|l=arch}} block by Arm. | 1 |

| 18:22, 16 February 2020 | cortex-m55 pipeline.svg (file) |  |

18 KB | Arm {{armh|Cortex-M55|l=arch}} pipeline by WikiChip. | 1 |

| 06:50, 15 February 2020 | wikichip-main-box-cha.jpg (file) |  |

73 KB | 1 | |

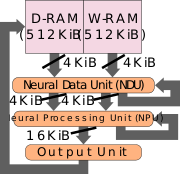

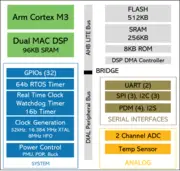

| 01:24, 12 February 2020 | ecm3532 block.png (file) |  |

287 KB | Eta Compute {{eta compute|ECM3532}} | 1 |

| 23:26, 11 February 2020 | etacompute-logo.png (file) | 47 KB | Eta Compute logo. | 1 | |

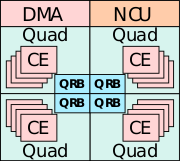

| 23:18, 10 February 2020 | ethos-n37,57,77 ce config.png (file) |  |

151 KB | Arm {{armh|Ethos}} N37,57,77 CE configurations. | 1 |

| 22:32, 10 February 2020 | arm ethos.svg (file) | 9 KB | Arm {{arm|Ethos}} | 1 | |

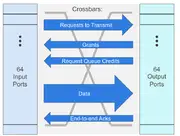

| 19:47, 8 February 2020 | rosetta crossbars.png (file) |  |

44 KB | Cray {{cray|Rosetta|l=arch}} crossbars. | 1 |

| 15:39, 8 February 2020 | cray slingshot switch.png (file) |  |

1.64 MB | Cray {{cray|Slingshot|l=wire}} | 1 |

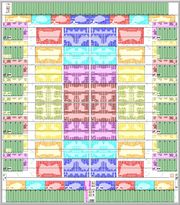

| 23:07, 7 February 2020 | cray rosetta die plot.jpg (file) |  |

1.88 MB | Cray {{cray|Rosetta|l=arch}} die plot. | 1 |

| 15:58, 5 February 2020 | mlp compute engine block diagram.svg (file) |  |

32 KB | arrow correction | 2 |

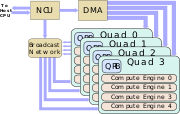

| 15:55, 5 February 2020 | mlp block diagram.svg (file) |  |

31 KB | Arm {{armh|MLP|l=arch}} block diagram by WikiChip. | 1 |

| 15:51, 5 February 2020 | mlp ple overview.svg (file) |  |

19 KB | 2 | |

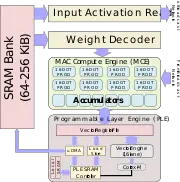

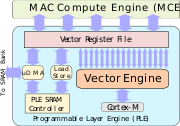

| 14:04, 5 February 2020 | mlp compute engine overview.svg (file) |  |

184 KB | {{armh|MLP|l=arch}} Compute Engine overview by WikiChip. | 1 |

| 16:03, 4 February 2020 | mlp overview.svg (file) |  |

15 KB | Arm {{armh|MLP|l=arch} over diagram by WikiChip. | 1 |

| 01:15, 2 February 2020 | sdm460-brief.pdf (file) |  |

325 KB | Snapdragon 460 PB. | 1 |

| 00:53, 2 February 2020 | sdm662-brief.pdf (file) |  |

325 KB | Snapdragon 662 PB. | 1 |

| 00:19, 2 February 2020 | sdm720g-brief.pdf (file) |  |

375 KB | Sanpdragon 720G PB. | 1 |

| 23:39, 1 February 2020 | sd 720g (front).png (file) |  |

72 KB | Snapdragon 720G, front. | 1 |

| 23:34, 1 February 2020 | sd 662 (front).png (file) |  |

91 KB | Snapdragon 662, front. | 1 |

| 23:33, 1 February 2020 | sd 460 (front).png (file) |  |

75 KB | Snapdragon 460, front. | 1 |

| 18:43, 1 February 2020 | S9200WK-Reference-Design-Guide.pdf (file) |  |

2.6 MB | Intel {{intel|Cascade Lake AP|l=arch}} S9200WK. | 1 |

| 12:05, 1 February 2020 | knights crest announcement.png (file) |  |

234 KB | Nervana {{nervana|Knights Crest|l=arch}} announcement. | 1 |

| 11:39, 1 February 2020 | ai hw summit supermicro ref pod rack.jpeg (file) |  |

2.09 MB | Nervana {{nervana|NNP}}-T ref pod rack. | 1 |

| 11:37, 1 February 2020 | ai hw summit supermicro ref pod.jpeg (file) |  |

3.18 MB | Nervana {{nervana|NNP}}-T reference pod. | 1 |

| 03:52, 1 February 2020 | supermicro nnp-i chassis.jpg (file) |  |

2.32 MB | Nervana {{nervana|NNP}}-I chassis by Supermicro. | 1 |

| 03:51, 1 February 2020 | nnp-i ruler.jpg (file) |  |

1.81 MB | Nervana {{nervana|NNP}}-I ruler. | 1 |

| 03:16, 1 February 2020 | 16433-1 NNP-announce NNP-I brief v5.1.pdf (file) |  |

414 KB | Nervan {{nervana|NNP}}-I PB. | 1 |

| 02:28, 1 February 2020 | 16433-1 NNP-announce NNP-T brief v4.3.pdf (file) |  |

695 KB | Intel Nervana {{nervana|NNP}}-T PB. | 1 |

| 03:30, 24 January 2020 | cha cns core die.png (file) |  |

103 KB | Centaur {{centtech|CHA|l=arch}} CNS core die. | 1 |

| 01:54, 24 January 2020 | cns mem subsys.svg (file) |  |

23 KB | WikiChip diagram of Centaur's {{centtech|CHA|l=arch}} CNS memory subsystem. | 1 |

| 01:32, 24 January 2020 | cns decode.svg (file) |  |

33 KB | WikiChip diagram of Centaur's {{centtech|CHA|l=arch}} CNS decode. | 1 |

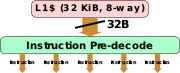

| 01:29, 24 January 2020 | cns icache.svg (file) |  |

12 KB | Centaur {{centtech|CHA|l=arch}} CNS instruction cache by diagram WikiChip. | 1 |

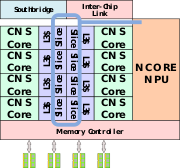

| 23:35, 23 January 2020 | cha soc overview.svg (file) |  |

44 KB | Centaur {{centtech|CHA|l=arch}} SoC overview by WikiChip. | 1 |

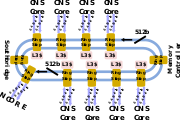

| 22:25, 23 January 2020 | cha ring.svg (file) |  |

60 KB | Centaur {{centtech|CHA|l=arch}} ring interconnect diagram by WikiChip. | 1 |

| 21:37, 23 January 2020 | ncore slices.svg (file) |  |

96 KB | Centaur {{centtech|CHA|l=arch}} diagram of the NCORE by WikiChip. | 1 |

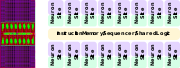

| 14:31, 23 January 2020 | cns block diagram.svg (file) |  |

119 KB | 2 | |

| 18:17, 22 January 2020 | cha soc ncore (2).png (file) |  |

6 KB | Centaur {{centtech|CHA|l=arch}} ncore. | 1 |

First page |

Previous page |

Next page |

Last page |