-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

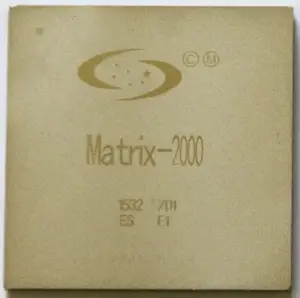

Matrix-2000 - NUDT

< nudt

Template:mpu Matrix-2000 is a 128-core many-core processor designed by NUDT and introduced in 2017. This chip was designed exclusively for China's Tianhe-2 supercomputer.

Facts about "Matrix-2000 - NUDT"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Matrix-2000 - NUDT#package + |

| base frequency | 1,200 MHz (1.2 GHz, 1,200,000 kHz) + |

| core count | 128 + |

| designer | NUDT + |

| first announced | 2015 + |

| first launched | 2017 + |

| full page name | nudt/matrix-2000 + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| ldate | 2017 + |

| main image |  + + |

| main image caption | Matrix-2000, package front + |

| max memory bandwidth | 143.1 GiB/s (146,534.4 MiB/s, 153.652 GB/s, 153,652.455 MB/s, 0.14 TiB/s, 0.154 TB/s) + |

| max memory channels | 8 + |

| model number | Matrix-2000 + |

| name | Matrix-2000 + |

| package | FCCLGA-4201 + |

| power dissipation | 240 W (240,000 mW, 0.322 hp, 0.24 kW) + |

| supported memory type | DDR4-2400 + |

| technology | CMOS + |

| thread count | 128 + |

| word size | 64 bit (8 octets, 16 nibbles) + |