From WikiChip

R-Car H2 - Renesas

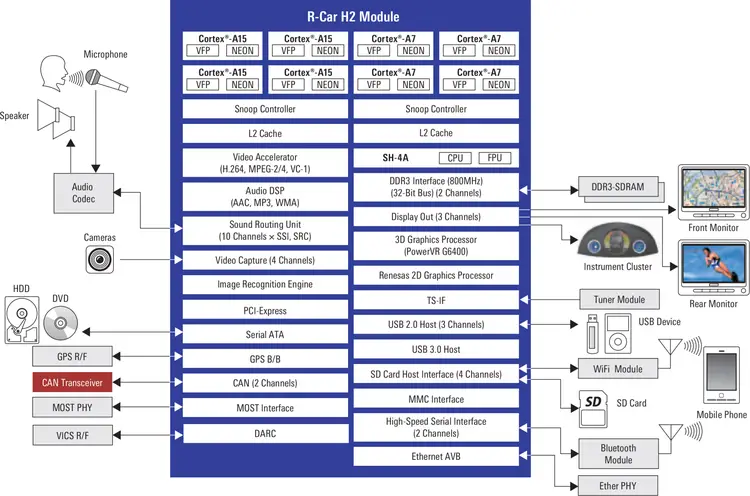

Template:mpu R-Car H2 is a high-end embedded nona-core SoC for the automotive industry introduced by Renesas in early 2013. The H2 incorporates four Cortex-A15 cores operating at 1.5 GHz, four Cortex-A7 cores operating at 1 GHz, and one SH-4A core operating at 780 MHz for real-time processing. This SoC incorporates Imagination's PowerVR G6400 GPU operating at 550 MHz and supports up to dual-channel DDR3-1600 memory.

Cache

- Main articles: Cortex-A15 § Cache and Cortex-A7 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions

- Flash ROM and SRAM, Data bus width: 8 or 16 bits

- PCI Express2.0 (1 lane)

- USB 3.0 Host interface × 1 port (wPHY)

- USB 2.0 Host interface × 3 port (wPHY)

- SD Host interface × 4 ch (SDXC, UHS-I)

- Multimedia card interface × 2 ch

- Serial ATA interface × 2 ch

- I²C bus interface × 8 ch

- Serial communication interface (SCIF) × 10 ch

- Quad serial peripheral interface (QSPI) × 1 ch (for boot)

- Clock-synchronized serial interface (MSIOF) × 4 ch (SPI/IIS)

- Ethernet controller (IEEE802.3u, RMII, without PHY)

Graphics

|

Integrated Graphics Information

|

||||||||||||

|

||||||||||||

Features

[Edit/Modify Supported Features]

|

Supported ARM Extensions & Processor Features

|

||||||||

|

||||||||

Block Diagram

Facts about "R-Car H2 - Renesas"

| has ecc memory support | false + |

| integrated gpu | PowerVR G6400 + |

| integrated gpu base frequency | 550 MHz (0.55 GHz, 550,000 KHz) + |

| integrated gpu designer | Imagination Technologies + |

| integrated gpu execution units | 1 + |

| l1$ size | 576 KiB (589,824 B, 0.563 MiB) + |

| l1d$ size | 288 KiB (294,912 B, 0.281 MiB) + |

| l1i$ size | 288 KiB (294,912 B, 0.281 MiB) + |

| l2$ size | 2.5 MiB (2,560 KiB, 2,621,440 B, 0.00244 GiB) + |

| max memory bandwidth | 11.92 GiB/s (12,206.08 MiB/s, 12.799 GB/s, 12,799.003 MB/s, 0.0116 TiB/s, 0.0128 TB/s) + |

| max memory channels | 2 + |

| supported memory type | DDR3-1600 + |