From WikiChip

Difference between revisions of "intel/core i7ee/i7-3960x"

m (Bot: replacing deprecated (and now obselete) {{mpu features}} with {{x86 features}}) |

m (Bot: Replacing old {{mpu expansions}} template with {{expansions}}) |

||

| Line 113: | Line 113: | ||

== Expansions == | == Expansions == | ||

| − | {{ | + | {{expansions |

| pcie revision = 2.00 | | pcie revision = 2.00 | ||

| pcie lanes = 40 | | pcie lanes = 40 | ||

Revision as of 14:54, 13 December 2017

Template:mpu The Core i7-3960X Extreme Edition was a 64-bit high-end hexa-core microprocessor introduced by Intel in late 2011. The i7-3960X operates at 3.3 GHz with turbo mode of up to 3.9 GHz. Fabricated in 32 nm based on the Sandy Bridge microarchitecture, this chip supports up to 64 GiB (DDR3) of memory and has a Thermal Design Power of 130 W.

Cache

- Main article: Sandy Bridge § Cache

| Cache Info [Edit Values] | ||

| L1I$ | 192 KiB 196,608 B 0.188 MiB |

6x32 KiB 8-way set associative (per core) |

| L1D$ | 192 KiB 196,608 B 0.188 MiB |

6x32 KiB 8-way set associative (per core) |

| L2$ | 1,536 KiB 1.5 MiB 1,572,864 B 0.00146 GiB |

6x256 KiB 8-way set associative (per core) |

| L3$ | 15 MiB 15,360 KiB 15,728,640 B 0.0146 GiB |

20-way set associative (shared) |

Graphics

This SoC has no integrated graphics processing unit.

Memory controller

| Integrated Memory Controller | |

| Type | DDR3-1066, DDR3-1333, DDR3-1600 |

| Controllers | 1 |

| Channels | 4 |

| ECC Support | No |

| Max bandwidth | 51.2 GB/s |

| Max memory | 64 GiB |

Expansions

|

Expansion Options

|

||||||||

|

||||||||

Features

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||

|

||||||||||||||||||||||||

- Note: VT-d support is only available on the C2 stepping version.

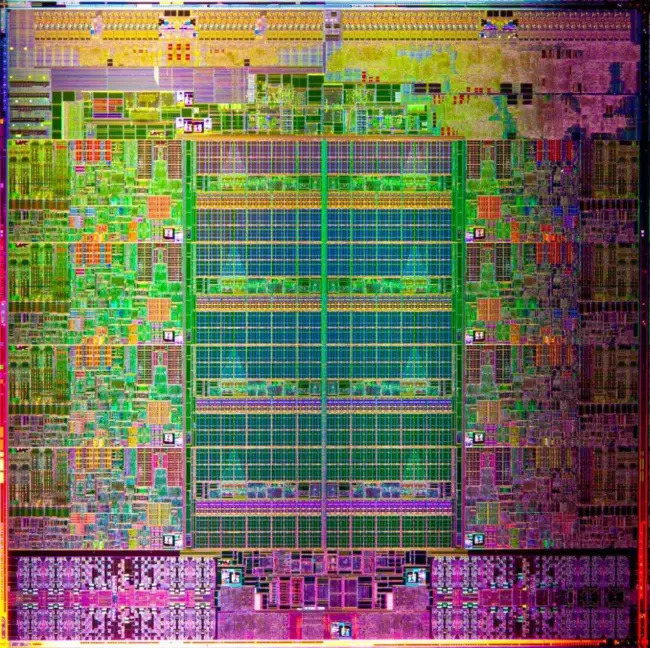

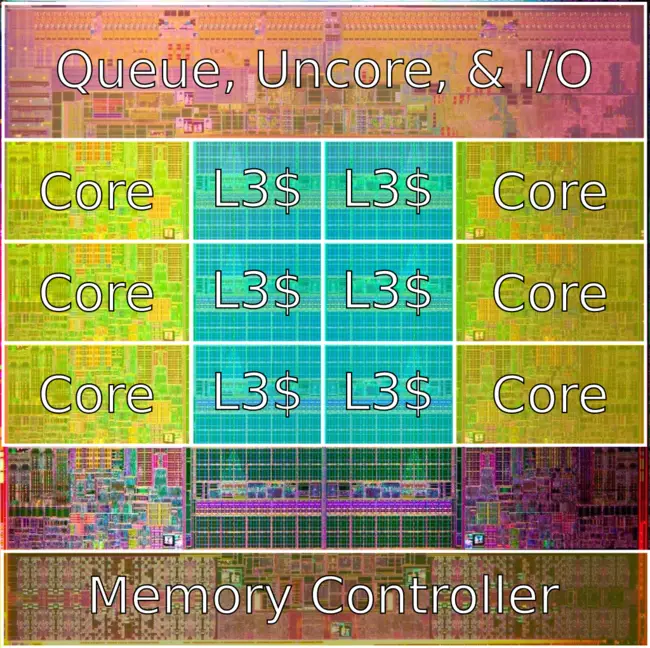

Die shot

- 6 cores (Note: die contains 2 fused off cores)

- 2,270,000,000 transistors

- 20.8 mm x 20.9 mm

- 434.72 mm²

See also

Facts about "Core i7-3960X Extreme Edition - Intel"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Core i7-3960X Extreme Edition - Intel#io + |

| base frequency | 3,300 MHz (3.3 GHz, 3,300,000 kHz) + |

| bus rate | 5,000 MT/s (5 GT/s, 5,000,000 kT/s) + |

| bus type | DMI 2.0 + |

| clock multiplier | 33 + |

| core count | 6 + |

| core name | Sandy Bridge E + |

| core stepping | C1 + and C2 + |

| cpuid | 206D7 + |

| designer | Intel + |

| die area | 434.72 mm² (0.674 in², 4.347 cm², 434,720,000 µm²) + |

| die length | 20.9 mm (2.09 cm, 0.823 in, 20,900 µm) + |

| die width | 20.8 mm (2.08 cm, 0.819 in, 20,800 µm) + |

| family | Core i7EE + |

| first announced | November 14, 2011 + |

| first launched | November 14, 2011 + |

| full page name | intel/core i7ee/i7-3960x + |

| has advanced vector extensions | true + |

| has extended page tables support | true + |

| has feature | Advanced Vector Extensions +, Advanced Encryption Standard Instruction Set Extension +, Hyper-Threading Technology +, Turbo Boost Technology 2.0 +, Enhanced SpeedStep Technology + and Extended Page Tables + |

| has intel enhanced speedstep technology | true + |

| has intel turbo boost technology 2 0 | true + |

| has locked clock multiplier | false + |

| has second level address translation support | true + |

| has simultaneous multithreading | true + |

| has x86 advanced encryption standard instruction set extension | true + |

| instance of | microprocessor + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 192 KiB (196,608 B, 0.188 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 192 KiB (196,608 B, 0.188 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 1.5 MiB (1,536 KiB, 1,572,864 B, 0.00146 GiB) + |

| l3$ description | 20-way set associative + |

| l3$ size | 15 MiB (15,360 KiB, 15,728,640 B, 0.0146 GiB) + |

| last order | September 26, 2014 + |

| last shipment | March 6, 2015 + |

| ldate | November 14, 2011 + |

| manufacturer | Intel + |

| market segment | Desktop + |

| max cpu count | 1 + |

| max memory | 65,536 MiB (67,108,864 KiB, 68,719,476,736 B, 64 GiB, 0.0625 TiB) + |

| max operating temperature | 66.8 °C + |

| max pcie lanes | 40 + |

| microarchitecture | Sandy Bridge + |

| min operating temperature | 0 °C + |

| model number | i7-3960X + |

| name | Core i7-3960X Extreme Edition + |

| part number | CM8061907184018 +, CM8061907184017 + and BX80619I73960X + |

| platform | 6 Series Chipset + |

| process | 32 nm (0.032 μm, 3.2e-5 mm) + |

| s-spec | SR0GW + and SR0KF + |

| s-spec (qs) | QBU9 + and QBE7 + |

| series | Core i7-3900 + |

| smp max ways | 1 + |

| tdp | 130 W (130,000 mW, 0.174 hp, 0.13 kW) + |

| technology | CMOS + |

| thread count | 12 + |

| transistor count | 2,270,000,000 + |

| turbo frequency (1 core) | 3,900 MHz (3.9 GHz, 3,900,000 kHz) + |

| turbo frequency (2 cores) | 3,900 MHz (3.9 GHz, 3,900,000 kHz) + |

| turbo frequency (3 cores) | 3,800 MHz (3.8 GHz, 3,800,000 kHz) + |

| turbo frequency (4 cores) | 3,800 MHz (3.8 GHz, 3,800,000 kHz) + |

| turbo frequency (5 cores) | 3,600 MHz (3.6 GHz, 3,600,000 kHz) + |

| turbo frequency (6 cores) | 3,600 MHz (3.6 GHz, 3,600,000 kHz) + |

| word size | 64 bit (8 octets, 16 nibbles) + |