From WikiChip

Difference between revisions of "renesas/r-car/e2"

| Line 14: | Line 14: | ||

|series=2nd Gen | |series=2nd Gen | ||

|frequency=1,000 MHz | |frequency=1,000 MHz | ||

| + | |frequency 2=780 MHz | ||

|isa=ARMv7 | |isa=ARMv7 | ||

|isa family=ARM | |isa family=ARM | ||

| Line 33: | Line 34: | ||

|package module 1={{packages/renesas/fcbga-501}} | |package module 1={{packages/renesas/fcbga-501}} | ||

}} | }} | ||

| + | '''R-Car E2''' is an entry-level embedded [[tri-core]] SoC designed by [[Renesas]] for the automotive industry and introduced in late 2014. The E2 incorporates two {{armh|Cortex-A7}} cores operating at 1 GHz along with a {{renesas|SH-4A}} core operating at 780 MHz for real-time processing. This chip includes an [[Imagination Technologies|Imagination]] {{imgtec|PowerVR SGX540}} [[GPU]] operating at 260 MHz and supports up to 2 GiB of dual-channel DDR3-1333 memory. | ||

| + | |||

| + | == Cache == | ||

| + | {{main|arm holdings/microarchitectures/cortex-a7#Memory_Hierarchy|l1=Cortex-A7 § Cache}} | ||

| + | {{cache size | ||

| + | |l1 cache=192 KiB | ||

| + | |l1i cache=96 KiB | ||

| + | |l1i break=3x32 KiB | ||

| + | |l1d cache=96 KiB | ||

| + | |l1d break=3x32 KiB | ||

| + | |l2 cache=512 KiB | ||

| + | |l2 break=1x512 KiB | ||

| + | }} | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=DDR3-1333 | ||

| + | |ecc=No | ||

| + | |max mem=2 GiB | ||

| + | |controllers=1 | ||

| + | |channels=2 | ||

| + | |width=32 bit | ||

| + | |max bandwidth=9.93 GiB/s | ||

| + | |bandwidth schan=4.97 GiB/s | ||

| + | |bandwidth dchan=9.93 GiB/s | ||

| + | }} | ||

| + | |||

| + | == Expansions == | ||

| + | * Flash ROM and SRAM, Data bus width: 8 or 16 bits | ||

| + | * USB 2.0 host interface × 2 ports (wPHY) | ||

| + | * SD host interface × 3 ch (SDXC, UHS-I) | ||

| + | * Multimedia card interface × 1 ch | ||

| + | * I²C bus interface × 8 ch | ||

| + | * Serial communication interface (SCIF) × 18 ch | ||

| + | * Quad serial peripheral interface (QSPI) × 1 ch (for boot) | ||

| + | * Clock-synchronized serial interface (MSIOF) × 3 ch (SPI/IIS) | ||

| + | * Ethernet AVB controller (IEEE802.1BA/802.1AS/802.1Qav/IEEE1722, GMII/MII, without PHY) | ||

| + | * Ethernet controller (IEEE802.3u, RMII, without PHY) | ||

| + | |||

| + | == Graphics == | ||

| + | {{integrated graphics | ||

| + | | gpu = PowerVR SGX540 | ||

| + | | designer = Imagination Technologies | ||

| + | | execution units = 1 | ||

| + | | max displays = 2 | ||

| + | | frequency = 260 MHz | ||

| + | }} | ||

| + | |||

| + | == Features == | ||

| + | {{arm features | ||

| + | |thumb=No | ||

| + | |thumb2=Yes | ||

| + | |thumbee=Yes | ||

| + | |vfpv1=No | ||

| + | |vfpv2=No | ||

| + | |vfpv3=No | ||

| + | |vfpv3-d16=No | ||

| + | |vfpv3-f16=No | ||

| + | |vfpv4=Yes | ||

| + | |vfpv4-d16=No | ||

| + | |vfpv5=No | ||

| + | |neon=Yes | ||

| + | |jazelle=No | ||

| + | |wmmx=No | ||

| + | |wmmx2=No | ||

| + | }} | ||

| + | |||

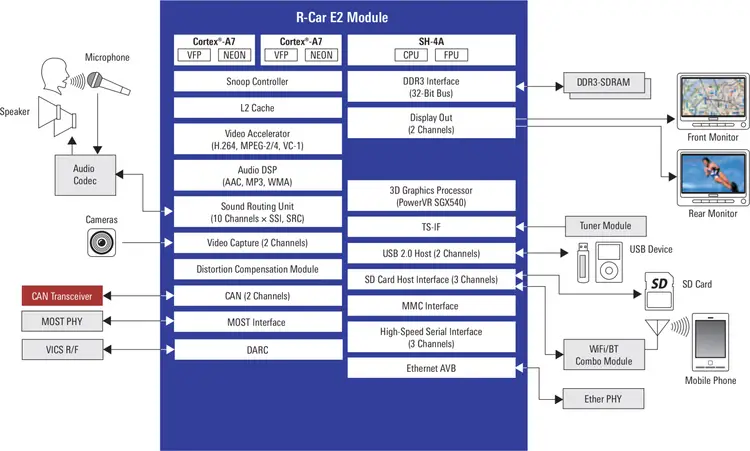

| + | == Block Diagram == | ||

| + | ::[[File:r-car e2 block.png|750px]] | ||

Revision as of 15:22, 22 July 2017

Template:mpu R-Car E2 is an entry-level embedded tri-core SoC designed by Renesas for the automotive industry and introduced in late 2014. The E2 incorporates two Cortex-A7 cores operating at 1 GHz along with a SH-4A core operating at 780 MHz for real-time processing. This chip includes an Imagination PowerVR SGX540 GPU operating at 260 MHz and supports up to 2 GiB of dual-channel DDR3-1333 memory.

Cache

- Main article: Cortex-A7 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Expansions

- Flash ROM and SRAM, Data bus width: 8 or 16 bits

- USB 2.0 host interface × 2 ports (wPHY)

- SD host interface × 3 ch (SDXC, UHS-I)

- Multimedia card interface × 1 ch

- I²C bus interface × 8 ch

- Serial communication interface (SCIF) × 18 ch

- Quad serial peripheral interface (QSPI) × 1 ch (for boot)

- Clock-synchronized serial interface (MSIOF) × 3 ch (SPI/IIS)

- Ethernet AVB controller (IEEE802.1BA/802.1AS/802.1Qav/IEEE1722, GMII/MII, without PHY)

- Ethernet controller (IEEE802.3u, RMII, without PHY)

Graphics

|

Integrated Graphics Information

|

||||||||||||

|

||||||||||||

Features

[Edit/Modify Supported Features]

|

Supported ARM Extensions & Processor Features

|

||||||||

|

||||||||

Block Diagram

Facts about "R-Car E2 - Renesas"

| has ecc memory support | false + |

| integrated gpu | PowerVR SGX540 + |

| integrated gpu base frequency | 260 MHz (0.26 GHz, 260,000 KHz) + |

| integrated gpu designer | Imagination Technologies + |

| integrated gpu execution units | 1 + |

| l1$ size | 192 KiB (196,608 B, 0.188 MiB) + |

| l1d$ size | 96 KiB (98,304 B, 0.0938 MiB) + |

| l1i$ size | 96 KiB (98,304 B, 0.0938 MiB) + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| max memory bandwidth | 9.93 GiB/s (10,168.32 MiB/s, 10.662 GB/s, 10,662.256 MB/s, 0.0097 TiB/s, 0.0107 TB/s) + |

| max memory channels | 2 + |

| supported memory type | DDR3-1333 + |