m (Bot: Automated text replacement (-\| electrical += Yes +)) |

m (Bot: corrected param) |

||

| Line 10: | Line 10: | ||

| model number = Z510PT | | model number = Z510PT | ||

| part number = CH80566EC005DT | | part number = CH80566EC005DT | ||

| − | | part number | + | | part number 2 = |

| s-spec = SLGPR | | s-spec = SLGPR | ||

| s-spec 2 = | | s-spec 2 = | ||

Revision as of 17:18, 30 June 2017

Template:mpu Z510PT is an ultra-low power 32-bit x86 microprocessor introduced by Intel in early 2009 specifically for Mobile Internet Devices (MID). The Z510PT, which is based on the Bonnell microarchitecture (Silverthorne core), is manufactured on a 45 nm process. This processor operates at 1.1 Ghz with a TDP of 2 W. The MPU features a legacy 400 MT/s front-side bus capable of communicating with the Poulsbo chipset in both low-power CMOS mode as well as normal GTL mode (which also works with other chipsets).

This model is identical to the Z510P but has an industrial operating temperature range. This processor has a TDP of 2 W when Hyper-Threading is disabled and 2.2 W when enabled.

Cache

- Main article: Bonnell § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller

This processor has no integrated memory controller.

Graphics

This processor has no integrated graphics.

Features

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||

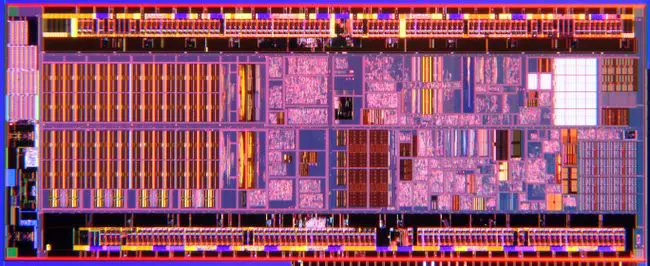

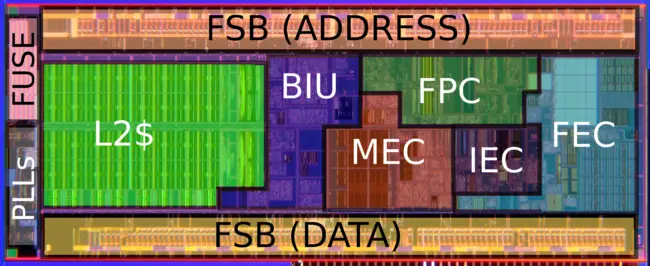

Die Shot

- See also: Bonnell § Silverthorne Die

- 45 nm process

- 9 metal layers

- 47,212,207 transistors

- 3.1 mm x 7.8 mm

- 24.18 mm² die size

Documents

Datasheet

| has feature | Hyper-Threading Technology + and Enhanced SpeedStep Technology + |

| has intel enhanced speedstep technology | true + |

| has simultaneous multithreading | true + |

| l1$ size | 56 KiB (57,344 B, 0.0547 MiB) + |

| l1d$ description | 6-way set associative + |

| l1d$ size | 24 KiB (24,576 B, 0.0234 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 32 KiB (32,768 B, 0.0313 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |