From WikiChip

Difference between revisions of "mediatek/helio/mt6797"

(Created page with "{{mediatek title|Helio X20 (MT6797)}} {{mpu | name = MediaTek Helio X20 | no image = yes | image = | image size = | caption...") |

|||

| Line 89: | Line 89: | ||

| package 0 height = | | package 0 height = | ||

}} | }} | ||

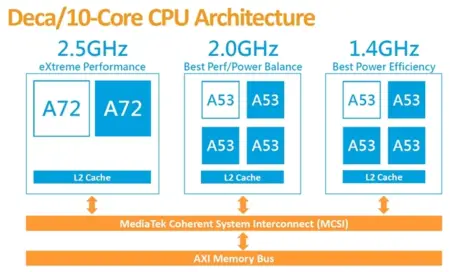

| − | '''Helio X20''' ('''MT6797''') is a {{arch|64}} [[deca-core]] [[ARM]] [[LTE]] system on a chip designed by [[MediaTek]] and introduced in early [[2015]]. This SoC incorporates 3 independent clusters of cores (called "Tri-Cluster Technology" by MediaTek) operating at varying degrees of performance designed for certain workloads (operating at 1.4 GHz, 2 GHz, and 2.5 GHz) and supports dual-channel LPDDR3-933. This SoC also incorporates a {{armh|Mali-T800 MP4}} [[IGP]] operating at | + | '''Helio X20''' ('''MT6797''') is a {{arch|64}} [[deca-core]] [[ARM]] [[LTE]] system on a chip designed by [[MediaTek]] and introduced in early [[2015]]. This SoC incorporates 3 independent clusters of cores (called "Tri-Cluster Technology" by MediaTek) operating at varying degrees of performance designed for certain workloads (operating at 1.4 GHz, 2 GHz, and 2.5 GHz) and supports dual-channel LPDDR3-933. This SoC also incorporates a {{armh|Mali-T800 MP4}} [[IGP]] operating at 780 MHz. The chip has a modem supporting [[LTE]] User Equipment (UE) category 6. |

| + | |||

| + | == Architecture == | ||

| + | The Helio X20 is designed is composed of 3 individual clusters of CPU cores depending on the level of performance required by the active applications. | ||

| + | |||

| + | * Extreme Performance - 2x {{armh|Cortex-A72|l=arch}} @ 2.5 GHz | ||

| + | * Performance/Power Balance - 4x {{armh|Cortex-A53|l=arch}} @ 2 GHz | ||

| + | * Power Efficiency - 4x {{armh|Cortex-A53|l=arch}} @ 1.4 GHz | ||

| + | |||

| + | [[File:mediatek helio x20.png|450px]] | ||

| + | |||

| + | == Cache == | ||

| + | {{main|arm holdings/microarchitectures/cortex-a53#Memory_Hierarchy|arm holdings/microarchitectures/cortex-a72#Memory_Hierarchy|l1=Cortex-A53 § Cache|l2=Cortex-A72 § Cache}} | ||

| + | {{empty section}} | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=DDR3-933 | ||

| + | |ecc=No | ||

| + | |max mem=4 GiB | ||

| + | |controllers=1 | ||

| + | |channels=2 | ||

| + | |max bandwidth=13.9 GiB/s | ||

| + | |bandwidth schan=6.95 GiB/s | ||

| + | |bandwidth dchan=13.9 GiB/s | ||

| + | }} | ||

| + | |||

| + | == Expansions == | ||

| + | {{expansions | ||

| + | |usb revision=2.0 | ||

| + | |usb revision 2=3.0 | ||

| + | |usb ports=8 | ||

| + | |uart=4 | ||

| + | |gp io=Yes | ||

| + | }} | ||

| + | |||

| + | == Graphics == | ||

| + | {{integrated graphics | ||

| + | | gpu = Mali-T880 | ||

| + | | device id = | ||

| + | | designer = ARM Holdings | ||

| + | | execution units = 4 | ||

| + | | max displays = | ||

| + | | max memory = | ||

| + | | frequency = 780 MHz | ||

| + | |||

| + | | output dsi = Yes | ||

| + | |||

| + | | max res dsi = 2560x1600 | ||

| + | |||

| + | | direct3d ver = 11.2 | ||

| + | | opencl ver = 1.2 | ||

| + | | opengl ver = 3.2 | ||

| + | | opengl es ver = 3.2 | ||

| + | | vulkan ver = 1.0 | ||

| + | | openvg ver = 1.1 | ||

| + | }} | ||

Revision as of 18:30, 4 December 2016

Template:mpu Helio X20 (MT6797) is a 64-bit deca-core ARM LTE system on a chip designed by MediaTek and introduced in early 2015. This SoC incorporates 3 independent clusters of cores (called "Tri-Cluster Technology" by MediaTek) operating at varying degrees of performance designed for certain workloads (operating at 1.4 GHz, 2 GHz, and 2.5 GHz) and supports dual-channel LPDDR3-933. This SoC also incorporates a Mali-T800 MP4 IGP operating at 780 MHz. The chip has a modem supporting LTE User Equipment (UE) category 6.

Architecture

The Helio X20 is designed is composed of 3 individual clusters of CPU cores depending on the level of performance required by the active applications.

- Extreme Performance - 2x Cortex-A72 @ 2.5 GHz

- Performance/Power Balance - 4x Cortex-A53 @ 2 GHz

- Power Efficiency - 4x Cortex-A53 @ 1.4 GHz

Cache

- Main articles: Cortex-A53 § Cache and Cortex-A72 § Cache

| This section is empty; you can help add the missing info by editing this page. |

Memory controller

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions

|

Expansion Options

|

||||||||||

|

||||||||||

Graphics

Facts about "Helio X20 (MT6797) - MediaTek"

| has ecc memory support | false + |

| integrated gpu | Mali-T880 + |

| integrated gpu base frequency | 780 MHz (0.78 GHz, 780,000 KHz) + |

| integrated gpu designer | ARM Holdings + |

| integrated gpu execution units | 4 + |

| max memory bandwidth | 13.9 GiB/s (14,233.6 MiB/s, 14.925 GB/s, 14,925.011 MB/s, 0.0136 TiB/s, 0.0149 TB/s) + |

| max memory channels | 2 + |

| supported memory type | DDR3-933 + |