(→Cache) |

|||

| Line 97: | Line 97: | ||

|l1i desc= | |l1i desc= | ||

|l1i extra= | |l1i extra= | ||

| − | |l1d cache=200 | + | |l1d cache=200 KiB |

| − | |l1d break=25x8 | + | |l1d break=25x8 KiB |

|l1d desc=4-way set associative | |l1d desc=4-way set associative | ||

|l1d extra=(write-back, per tile) | |l1d extra=(write-back, per tile) | ||

| − | |l2 cache=1. | + | |l2 cache=1.5 MiB |

| − | |l2 break=25x64 | + | |l2 break=25x64 KiB |

|l2 desc=4-way set associative | |l2 desc=4-way set associative | ||

|l2 extra=(per tile) | |l2 extra=(per tile) | ||

Revision as of 01:02, 21 September 2016

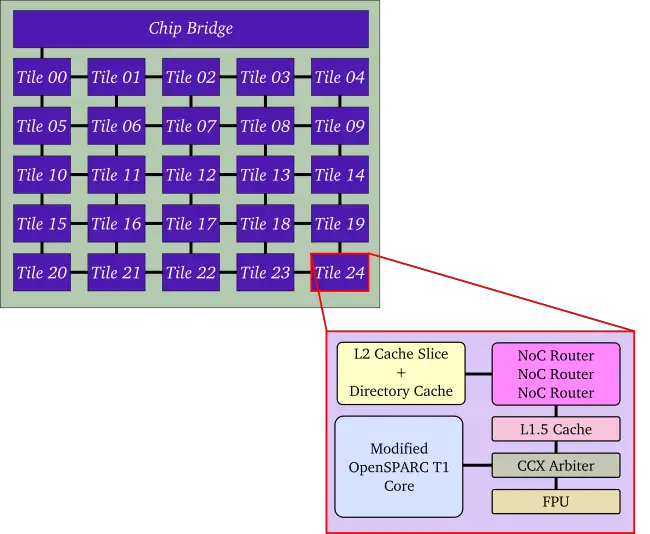

Template:mpu Piton is a 64-bit many-core microprocessor developed by Princeton's Parallel Computing Group and announced in August of 2016. The MPPA chip contains 25 modified OpenSPARC T1 cores (an implementation of SPARC V9). The chip, which was manufactured on IBM's 32 nm SOI process, operates at 1 GHz. The chip was presented in August 2016 at the Hot Chips 28.

Architecture

The chip is designed as a massively parallel processor array, with 25 cores ("tiles") arranged as a 2D grid of 5 by 5. Each core is a modified OpenSPARC T1 which implements SPARC V9 capable of booting a standard OS. Piton implements a 64-bit network on chip (NoC) interconnect made of 3 physical networks operating with a 1 cycle/hop latency.

Tiles

Piton is made of an array of tiles in a grid of 5x5. Each tile is composed of a modified OpenSPARC T1 core (+L1$), an L1.5 cache, L2 cache, a floating-point unit (FPU), a CPU Cache-Crossbar (CCX) arbiter, and three network on chip (NoC) routers.

Cache

Pitons uses a distributed write-back L2$ model that implements a directory-based MESI protocol - adhering to OpenSPARC's total store order (TSO) model. Each tile contains 64 KB slice of the L2 cache and an attached cache directory. The L2 cache is inclusive of both the L1.5$ and the L1$. Note that the L1.5 is called as such because the OpenSPARC T1 core already implements an 8 KB L1d$ and 16 KB L1i$ which are tightly coupled with the pipeline and was thus only modified to work in a scaleable multi-core environment. The L1.5$ acts as a middleman between the OpenSPARC T1's crossbar protocol and the Piton's NoC. It relays requests and replies to and from the core through CCX.

| Cache Info [Edit Values] | ||

| L1D$ | 200 KiB 204,800 B 0.195 MiB |

25x8 KiB 4-way set associative (write-back, per tile) |

| L2$ | 1.5 MiB 1,536 KiB 1,572,864 B 0.00146 GiB |

25x64 KiB 4-way set associative (per tile) |

Network On-chip (NoC)

Piton implements 3 physical networks on chip (NoC) that provide all the communication between the tiles, deliver I/O and memory traffic, and pass inter-core interrupts. Piton implements 3 physical neworks - each consisting of two 64-bit uni-directional links (one in each direction). Packets routing implements dimension-order routing. Each packet reserves 29 bits for core address, allowing a theoretical network size of 500 million cores. The three NoCs have descending priorities - i.e. NoC3 has the highest priority, followed by NoC2, followed by NoC1 with the lowest priority.

Documents

- Jonathan Balkind, Michael McKeown, Yaosheng Fu, Tri Nguyen, Yanqi Zhou, Alexey Lavrov, Mohammad Shahrad, Adi Fuchs, Samuel Payne, Xiaohua Liang, Matthew Matl, David Wentzlaff. OpenPiton: An open source manycore research framework. In Proceedings of the Twenty-First International Conference on Architectural Support for Programming Languages and Operating Systems 2016 Mar 25 (pp. 217-232). ACM.

- Michael McKeown, Yaosheng Fu, Tri Nguyen, Yanqi Zhou, Jonathan Balkind, Alexey Lavrov, Mohammad Shahrad, Samuel Payne, and David Wentzlaf. Piton: A 25-core Academic Manycore Research Processor

- OpenPit OpenPiton Microarchitecture Specification. Hot Chips 28. August 23, 2016.

External links

| l1d$ description | 4-way set associative + |

| l1d$ size | 200 KiB (204,800 B, 0.195 MiB) + |

| l2$ description | 4-way set associative + |

| l2$ size | 1.5 MiB (1,536 KiB, 1,572,864 B, 0.00146 GiB) + |