From WikiChip

Difference between revisions of "amd/microarchitectures/navi"

(→Comparison of RDNA chips) |

(→Comparison of RDNA chips) |

||

| Line 102: | Line 102: | ||

=== Comparison of RDNA chips === | === Comparison of RDNA chips === | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

{| class="wikitable" cellpadding="3px" style="border: 1px solid black; border-spacing: 0px; width: 100%; text-align:center;" | {| class="wikitable" cellpadding="3px" style="border: 1px solid black; border-spacing: 0px; width: 100%; text-align:center;" | ||

| Line 307: | Line 119: | ||

| 740M<hr>760M<hr>780M | | 740M<hr>760M<hr>780M | ||

| 740M<hr>760M<hr>780M | | 740M<hr>760M<hr>780M | ||

| − | | Radeon<br>880M<hr>890M | + | | Radeon<br>880M<hr>890M <ref>{{cite book |title=AMD Details the Radeon 890M RDNA 3.5 iGPU of "Strix Point" a bit More |url=https://www.techpowerup.com/324874/amd-details-the-radeon-890m-rdna-3-5-igpu-of-strix-point-a-bit-more |access-date=September 7, 2024 |website=TechPowerUp}}</ref> |

| 8040S<hr>8050S<hr>8060S | | 8040S<hr>8050S<hr>8060S | ||

| Radeon<br>840M<hr>860M | | Radeon<br>840M<hr>860M | ||

| Line 319: | Line 131: | ||

| Phoenix | | Phoenix | ||

| Hawk Point | | Hawk Point | ||

| − | | ''Strix Point'' <ref>{{cite book |title=AMD Strix Point GPU Specs |url=https://www.techpowerup.com/gpu-specs/amd-strix-point.g1079 | + | | ''Strix Point'' <ref>{{cite book |title=AMD Strix Point GPU Specs |url=https://www.techpowerup.com/gpu-specs/amd-strix-point.g1079 |access-date=September 7, 2024 |website=TechPowerUp}}</ref> |

| ''Strix Halo'' <ref>{{cite book |title=AMD Strix Halo GPU Specs |url=https://www.techpowerup.com/gpu-specs/amd-strix-halo.g1096 |access-date=2025-10-09 |website=TechPowerUp}}</ref> | | ''Strix Halo'' <ref>{{cite book |title=AMD Strix Halo GPU Specs |url=https://www.techpowerup.com/gpu-specs/amd-strix-halo.g1096 |access-date=2025-10-09 |website=TechPowerUp}}</ref> | ||

|''Krackan Point'' <ref>{{cite book |title=AMD Krackan Point GPU Specs |url=https://www.techpowerup.com/gpu-specs/amd-krackan-point.g1092 |access-date=2025-10-09 |website=TechPowerUp}}</ref> | |''Krackan Point'' <ref>{{cite book |title=AMD Krackan Point GPU Specs |url=https://www.techpowerup.com/gpu-specs/amd-krackan-point.g1092 |access-date=2025-10-09 |website=TechPowerUp}}</ref> | ||

| Line 360: | Line 172: | ||

! Die size (mm<sup>2</sup>) | ! Die size (mm<sup>2</sup>) | ||

| || || || || | | || || || || | ||

| − | | colspan="2" | 178 | + | | colspan="2" | 178 |

| + | | 232 || 232 / 308 || TBA | ||

|- | |- | ||

! Workgroup processors <br>(WGP) | ! Workgroup processors <br>(WGP) | ||

| || || | | || || | ||

| − | | || || || | + | | || || || |

| + | | 8 || 20 || 4 | ||

|- | |- | ||

! Compute units (CU) | ! Compute units (CU) | ||

| || || | | || || | ||

| − | | || | + | | || |

| + | | 4 (Z1)<hr>8<hr>12 (Z1E) || 4<hr>8<hr>12 | ||

| 12<hr>16 || 16<hr>32<hr>40 || 4<hr>8 | | 12<hr>16 || 16<hr>32<hr>40 || 4<hr>8 | ||

|- | |- | ||

! Stream processors <br>(Cores) | ! Stream processors <br>(Cores) | ||

| 384<hr>768 || 128 || 128 | | 384<hr>768 || 128 || 128 | ||

| − | | 384<hr>768 || 128 | + | | 384<hr>768 || 128 |

| + | | 256<hr>512<hr>768 || 256<hr>512<hr>768 | ||

| 768<hr>1024 || 1024<hr>2048<hr>2560 || 256<hr>512 | | 768<hr>1024 || 1024<hr>2048<hr>2560 || 256<hr>512 | ||

|- | |- | ||

! Texture mapping units <br>(TMU) | ! Texture mapping units <br>(TMU) | ||

| 24<hr>48 || 8 || 8 | | 24<hr>48 || 8 || 8 | ||

| − | | 24<hr>48 || 8 | + | | 24<hr>48 || 8 |

| + | | 16<hr>32<hr>48 || 16<hr>32<hr>48 | ||

| 48<hr>64 || 64<hr>128<hr>160 || 16<hr>32 | | 48<hr>64 || 64<hr>128<hr>160 || 16<hr>32 | ||

|- | |- | ||

! Render output units <br>(ROP) | ! Render output units <br>(ROP) | ||

| 16<hr>32 || 8 || 4 | | 16<hr>32 || 8 || 4 | ||

| − | | 16<hr>32 || 4 | + | | 16<hr>32 || 4 |

| − | | 24<hr>32 || 32< | + | | 8<hr>16<hr>32 || 8<hr>16<hr>32 |

| + | | 24<hr>32 || 32<hr>64<hr>80 || 8<hr>16 | ||

|- | |- | ||

! RT accelerators | ! RT accelerators | ||

| || || | | || || | ||

| − | | || || | | + | | || |

| + | | 4 (Z1)<hr>8<hr>12 (Z1E) || 4<hr>8<hr>12 | ||

| 12<hr>16 || 16<hr>32<hr>40 || 4<hr>8 | | 12<hr>16 || 16<hr>32<hr>40 || 4<hr>8 | ||

|- | |- | ||

| Line 398: | Line 217: | ||

! L0 cache (KB) | ! L0 cache (KB) | ||

| colspan="5" | 32 KB per WGP (Workgroup processor) | | colspan="5" | 32 KB per WGP (Workgroup processor) | ||

| − | | colspan=" | + | | colspan="2" | 64 KB per WGP |

| + | | colspan="3" | 64 KB per WGP | ||

|- | |- | ||

! L1 cache (KB) | ! L1 cache (KB) | ||

| colspan="5" | 128 KB per SA (Shader array) | | colspan="5" | 128 KB per SA (Shader array) | ||

| − | | colspan=" | + | | colspan="2" | 256 KB per SA |

| + | | colspan="3" | 256 KB per SA | ||

|- | |- | ||

! L2 cache (MB) | ! L2 cache (MB) | ||

| || || | | || || | ||

| − | | || || || | + | | || || 2 || 2 |

| + | | 2 || 8 || 2 | ||

|- | |- | ||

! L3 cache (MB) | ! L3 cache (MB) | ||

| || || | | || || | ||

| − | | || || || | + | | || || 0 / 16 (Z1)|| 0 |

| + | | 0 || 64 || 0 | ||

|- | |- | ||

! Memory type | ! Memory type | ||

| Line 418: | Line 241: | ||

| DDR5 /<br>LPDDR5 | | DDR5 /<br>LPDDR5 | ||

| GDDR6 | | GDDR6 | ||

| − | | colspan=" | + | | colspan="2" | DDR5 / LPDDR5(X) |

| + | | colspan="3" | DDR5 / LPDDR5(X) | ||

|- | |- | ||

! Memory bus (bits) | ! Memory bus (bits) | ||

| − | | colspan="3" | 128 | + | | colspan="3" | 128 |

| + | | colspan="2" | 128 | ||

| + | | colspan="2" | 128 | ||

| 128 || 128 / 256 || 128 | | 128 || 128 / 256 || 128 | ||

|- | |- | ||

! Display Core Next | ! Display Core Next | ||

| − | | colspan="2" | || | + | | colspan="2" | || || || |

| − | | || || colspan="2" | | + | | colspan="2" | |

| + | | 3.1.4 || 3.5.0 || 3.5.0 | ||

|- | |- | ||

! Video Core Next | ! Video Core Next | ||

| − | | colspan="2" | || | + | | colspan="2" | || || || |

| − | | || || colspan="2" | | + | | colspan="2" | |

| + | | 4.0.2 || 4.0.5 || 4.0.5 | ||

|- | |- | ||

! Launch | ! Launch | ||

| January <br>2022 | | January <br>2022 | ||

| colspan="2" | September <br>2022 | | colspan="2" | September <br>2022 | ||

| − | | colspan=" | + | | colspan="2" | January <br>2023 |

| − | | December <br>2023 | + | | January <br>2023 || December <br>2023 |

| − | | July <br>2024 | + | | July <br>2024 || January <br>2025 || March <br>2025 |

| − | | January <br>2025 | ||

| − | | March <br>2025 | ||

|} | |} | ||

Revision as of 11:10, 6 November 2025

| Edit Values | |

| Navi µarch | |

| General Info | |

| Arch Type | GPU |

| Designer | AMD |

| Manufacturer | TSMC |

| Introduction | 2018 |

| Process | 7 nm |

| Succession | |

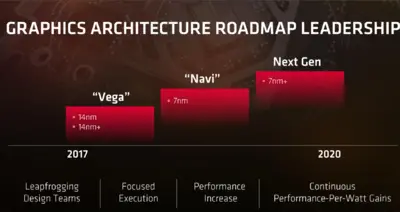

Navi is the successor to Vega, a 7 nm high-performance graphics processing unit microarchitecture for the gaming market.

Contents

Architecture

Key changes from Vega

- 7 nm process (from 14 nm)

- Architecture

- Models

- Navi • Radeon RX 5000 series

- Navi 2x • Radeon RX 6000 series

- Navi 3x • Radeon RX 7000 series

Generation

- AMD Navi II IGP (7)

| Name | Family | Bus | Memory | GPU Clock | Memory Clock | Cores / TMUs / ROPs | Release |

|---|---|---|---|---|---|---|---|

| Radeon 610M | Mendocino | PCIe 4.0 x8 | System Shared / DDR5 | 1900 MHz | System Shared | 128 / 8 / 4 | Sep 20, 2022 |

| Radeon 610M | Dragon Range | PCIe 4.0 x8 | System Shared / GDDR6 | 2200 MHz | System Shared | 128 / 8 / 4 | Jan 3, 2023 |

| Radeon 660M | Rembrandt | PCIe 4.0 x8 | System Shared / DDR5 | 1900 MHz | System Shared | 384 / 24 / 16 | Jan 4, 2022 |

| Radeon 660M | Rembrandt+ | PCIe 4.0 x8 | System Shared / DDR5 | 1900 MHz | System Shared | 384 / 24 / 16 | Jan 3, 2023 |

| Radeon 680M | Rembrandt | PCIe 4.0 x8 | System Shared / DDR5 | 2200 MHz | System Shared | 768 / 48 / 32 | Jan 4, 2022 |

| Radeon 680M | Rembrandt+ | PCIe 4.0 x8 | System Shared / DDR5 | 2200 MHz | System Shared | 768 / 48 / 32 | Jan 3, 2023 |

| Radeon Graphics 128SP | Raphael | PCIe 4.0 x8 | System Shared / GDDR6 | 2200 MHz | System Shared | 128 / 8 / 8 | Sep 27, 2022 |

- AMD Navi III IGP (12)

| Name | Family | Bus | Memory | GPU Clock | Memory Clock | Cores / TMUs / ROPs | Release |

|---|---|---|---|---|---|---|---|

| Radeon 740M | Phoenix | PCIe 4.0 x8 | System Shared / DDR5 | 2500 MHz | System Shared | 256 / 16 / 8 | Jan 4th, 2023 |

| Radeon 740M | Hawk Point | PCIe 4.0 x8 | System Shared / DDR5 | 2800 MHz | System Shared | 256 / 16 / 8 | Dec 6, 2023 |

| Radeon 740M | Phoenix2 | PCIe 4.0 x8 | System Shared / DDR5 | 2800 MHz | System Shared | 256 / 16 / 8 | Jan 31, 2024 |

| Radeon 760M | Phoenix | PCIe 4.0 x8 | System Shared / DDR5 | 2600 MHz | System Shared | 512 / 32 / 16 | Jan 4, 2023 |

| Radeon 760M | Hawk Point | PCIe 4.0 x8 | System Shared / DDR5 | 2600 MHz | System Shared | 512 / 32 / 16 | Dec 6, 2023 |

| Radeon 760M | Phoenix | PCIe 4.0 x8 | System Shared / DDR5 | 2600 MHz | System Shared | 512 / 32 / 16 | Jan 31, 2024 |

| Radeon 780M | Phoenix | PCIe 4.0 x8 | System Shared / DDR5 | 2700 MHz | System Shared | 768 / 48 / 32 | Jan 4, 2023 |

| Radeon 780M | Hawk Point | PCIe 4.0 x8 | System Shared / DDR5 | 2700 MHz | System Shared | 768 / 48 / 32 | Dec 6, 2023 |

| Radeon 780M | Phoenix | PCIe 4.0 x8 | System Shared / DDR5 | 2900 MHz | System Shared | 768 / 48 / 32 | Jan 31, 2024 |

| Radeon 860M | Krackan Point | PCIe 4.0 x8 | System Shared / DDR5 | 3000 MHz | System Shared | 512 / 32 / 8 | Mar 15, 2025 |

| Radeon 880M | Strix Point | PCIe 4.0 x8 | System Shared / DDR5 | 2900 MHz | System Shared | 768 / 48 / 16 | Jul 15, 2024 |

| Radeon 890M | Strix Point | PCIe 4.0 x8 | System Shared / DDR5 | 2900 MHz | System Shared | 1024 / 64 / 32 | Jul 15, 2024 |

Comparison of RDNA chips

| Microarchitecture | RDNA 2 (Navi II) | RDNA 3 (Navi III) | RDNA 3.5 (Navi III) | |||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Introduced | Radeon 660M 680M |

Radeon Graphics 128SP |

Radeon 610M |

Radeon 660M 680M |

Radeon 610M |

740M 760M 780M |

740M 760M 780M |

Radeon 880M 890M [1] |

8040S 8050S 8060S |

Radeon 840M 860M |

| Code name | Rembrandt | Raphael | Mendocino | Rembrandt-R | Dragon Range | Phoenix | Hawk Point | Strix Point [2] | Strix Halo [3] | Krackan Point [4] |

| Mobile APU | Ryzen 6000 |

Ryzen 7000 |

Ryzen 7020 |

Ryzen 7035 |

Ryzen 7045 |

Ryzen 7040 (Z1) |

Ryzen 8040 |

Ryzen | Ryzen | Ryzen |

| LLVM target [5] [6] | gfx1035 | gfx1036 | gfx1037 | gfx1035 | gfx1037 | gfx1103 | gfx1150 (1) | gfx1151 | gfx1152 | |

| Fab process | TSMC N6 | TSMC N4 | TSMC N4P | |||||||

| Package | Monolithic | Monolithic | Semi-MCM | Monolithic | ||||||

| Die size (mm2) | 178 | 232 | 232 / 308 | TBA | ||||||

| Workgroup processors (WGP) |

8 | 20 | 4 | |||||||

| Compute units (CU) | 4 (Z1) 8 12 (Z1E) |

4 8 12 |

12 16 |

16 32 40 |

4 8 | |||||

| Stream processors (Cores) |

384 768 |

128 | 128 | 384 768 |

128 | 256 512 768 |

256 512 768 |

768 1024 |

1024 2048 2560 |

256 512 |

| Texture mapping units (TMU) |

24 48 |

8 | 8 | 24 48 |

8 | 16 32 48 |

16 32 48 |

48 64 |

64 128 160 |

16 32 |

| Render output units (ROP) |

16 32 |

8 | 4 | 16 32 |

4 | 8 16 32 |

8 16 32 |

24 32 |

32 64 80 |

8 16 |

| RT accelerators | 4 (Z1) 8 12 (Z1E) |

4 8 12 |

12 16 |

16 32 40 |

4 8 | |||||

| AI accelerators | 32 | 80 | 16 | |||||||

| L0 cache (KB) | 32 KB per WGP (Workgroup processor) | 64 KB per WGP | 64 KB per WGP | |||||||

| L1 cache (KB) | 128 KB per SA (Shader array) | 256 KB per SA | 256 KB per SA | |||||||

| L2 cache (MB) | 2 | 2 | 2 | 8 | 2 | |||||

| L3 cache (MB) | 0 / 16 (Z1) | 0 | 0 | 64 | 0 | |||||

| Memory type | DDR5 / LPDDR5 |

GDDR6 | LPDDR5 | DDR5 / LPDDR5 |

GDDR6 | DDR5 / LPDDR5(X) | DDR5 / LPDDR5(X) | |||

| Memory bus (bits) | 128 | 128 | 128 | 128 | 128 / 256 | 128 | ||||

| Display Core Next | 3.1.4 | 3.5.0 | 3.5.0 | |||||||

| Video Core Next | 4.0.2 | 4.0.5 | 4.0.5 | |||||||

| Launch | January 2022 |

September 2022 |

January 2023 |

January 2023 |

December 2023 |

July 2024 |

January 2025 |

March 2025 | ||

References

- AMD 2017 Financial Analyst Day, May 16, 2017

See also

Facts about "Navi - Microarchitectures - AMD"

| codename | Navi + |

| designer | AMD + |

| first launched | 2018 + |

| full page name | amd/microarchitectures/navi + |

| instance of | microarchitecture + |

| manufacturer | TSMC + |

| microarchitecture type | GPU + |

| name | Navi + |

| process | 7 nm (0.007 μm, 7.0e-6 mm) + |