From WikiChip

Difference between revisions of "ibm/microarchitectures/power10"

(Edit) |

|||

| Line 25: | Line 25: | ||

== Process technology == | == Process technology == | ||

| − | POWER10 is planned to make use of [[ | + | POWER10 is planned to make use of [[TSMC]]'s DUV-based N7P process. |

== Architecture == | == Architecture == | ||

Revision as of 03:03, 5 December 2019

| Edit Values | |

| POWER10 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | IBM |

| Manufacturer | TSMC |

| Introduction | 2021 |

| Process | 7 nm |

| Pipeline | |

| Type | Superscalar |

| Speculative | Yes |

| Reg Renaming | Yes |

| Succession | |

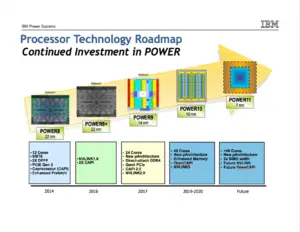

POWER10 is IBM's successor to POWER9, a 7 nm microarchitecture for Power-based server microprocessors expected to launch around the 2020 timeframe. POWER10-based processors are branded under the POWER family.

Process technology

POWER10 is planned to make use of TSMC's DUV-based N7P process.

Architecture

Key changes from POWER9

- 7 nm process (from 14 nm)

- 48 cores (from 24)

Facts about "POWER10 - Microarchitectures - IBM"

| codename | POWER10 + |

| designer | IBM + |

| first launched | 2021 + |

| full page name | ibm/microarchitectures/power10 + |

| instance of | microarchitecture + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | POWER10 + |

| process | 7 nm (0.007 μm, 7.0e-6 mm) + |