From WikiChip

Difference between revisions of "amd/microarchitectures/k6"

Chlamchowder (talk | contribs) (add a block diagram) |

(add tables) |

||

| Line 10: | Line 10: | ||

| process = 350 nm | | process = 350 nm | ||

| process 2 = 250 nm | | process 2 = 250 nm | ||

| − | |isa=x86-32 | + | | isa=x86-32 |

| − | |||

| succession = Yes | | succession = Yes | ||

| predecessor = K5 | | predecessor = K5 | ||

| Line 18: | Line 17: | ||

| successor link = amd/microarchitectures/k6-2 | | successor link = amd/microarchitectures/k6-2 | ||

}} | }} | ||

| − | '''K6''' was the [[microarchitecture]] for [[AMD]]'s {{amd|K6}} line of microprocessors as a successor to the {{\\|K5}}. Contrary to its namesake, K6 design is entirely [[NexGen]]'s and not based on {{\\|K5}}. Launched in early [[1997]], the K6 microarchitecture provided the superior performance AMD needed to become a viable competitor to Intel (performance {{\\|K5}} failed to deliver). K6 was superseded by {{\\|K6-2}} in 1998. | + | |

| + | '''K6''' was the [[microarchitecture]] for [[AMD]]'s {{amd|K6}} line of microprocessors as a successor to the {{\\|K5}}. Contrary to its namesake, K6 design is entirely [[NexGen]]'s and not based on {{\\|K5}}. Launched in early [[1997]], the K6 microarchitecture provided the superior performance AMD needed to become a viable competitor to Intel (performance {{\\|K5}} failed to deliver). K6 was superseded by {{\\|K6-2}} in [[1998]]. | ||

== Architecture == | == Architecture == | ||

| Line 33: | Line 33: | ||

*** Does not store target addresses. Target addresses are calculated during instruction decode | *** Does not store target addresses. Target addresses are calculated during instruction decode | ||

** 16-entry branch target cache | ** 16-entry branch target cache | ||

| − | *** Caches 16 bytes of instructions at the branch target, and supplies that directly to the decoders to avoid a 1-cycle penalty | + | *** Caches 16 bytes of instructions at the branch target, and supplies that directly <br>to the decoders to avoid a 1-cycle penalty |

** 16-entry return address stack | ** 16-entry return address stack | ||

* 32K 2-way L1 Instruction Cache | * 32K 2-way L1 Instruction Cache | ||

| Line 64: | Line 64: | ||

** 128 entry TLB | ** 128 entry TLB | ||

** Load unit has 2-cycle latency | ** Load unit has 2-cycle latency | ||

| − | |||

| − | == | + | === Am386/Am486/Am5x86/K5/K6/K7/K8 === |

| − | {{ | + | <!--{| class="wikitable sortable" cellpadding="3px" style="border: 1px solid black; border-spacing: 0px; width: 100%; text-align:center;" {| class="wikitable mw-datatable" style="margin:0.2em auto; text-align:center; min-width:70em;"--> |

| + | {|class="wikitable sortable" style="text-align: center; width: 100%; font-size: 100%;" | ||

| + | |- | ||

| + | ! [[Microarchitecture|Architecture]] | ||

| + | ! [[technology node|Process]] <br>(nm) | ||

| + | ! Family | ||

| + | ! Release <br>date | ||

| + | ! Code name | ||

| + | ! Model group | ||

| + | ! Cores | ||

| + | ! Clock rate <br>(MHz) | ||

| + | |- | ||

| + | !| {{amd|K5}} | ||

| + | | [[500 nm]]<hr>[[350 nm]] | ||

| + | | [[AMD K5]] | ||

| + | | 1996 | ||

| + | | SSA/5, 5k86 | ||

| + | | | ||

| + | | 1 | ||

| + | | 75–133 | ||

| + | |- | ||

| + | ! rowspan=3 | {{amd|K6}} | ||

| + | | [[350 nm]]<hr>[[250 nm]] | ||

| + | | [[AMD K6]] | ||

| + | | 1997<hr>1998 | ||

| + | | 6k86 (NX686) <!--(Model 6)--><hr>{{amd|Little Foot|l=core}} | ||

| + | | AMD-K6-166 ÷ 233 <hr>AMD-K6/233 ÷ 300 <!--(NX686/Little Foot)--> | ||

| + | | rowspan="3" | 1 | ||

| + | | 166–300 | ||

| + | |- | ||

| + | | rowspan=2 | [[250 nm]]<hr>[[180 nm]] | ||

| + | | [[AMD]] {{amd|K6-2}}(+) | ||

| + | | 1999 | ||

| + | | {{amd|Chomper|l=core}} <br>(Extended, Mobile) | ||

| + | | K6-2 (Chompers/CXT)<br>K6-2-P (Mobile K6-2) | ||

| + | | 166–550 | ||

| + | |- | ||

| + | | [[AMD]] {{amd|K6-III}}(+) | ||

| + | | 2001 | ||

| + | | {{amd|Sharptooth|l=core}} | ||

| + | | K6-III (Sharptooth)<br>K6-III-P | ||

| + | | 400–550 | ||

| + | |- | ||

| + | |} | ||

== All K6 Chips == | == All K6 Chips == | ||

| Line 96: | Line 138: | ||

{{table count|col=6|ask=[[Category:microprocessor models by amd]] [[instance of::microprocessor]] [[microarchitecture::K6]]}} | {{table count|col=6|ask=[[Category:microprocessor models by amd]] [[instance of::microprocessor]] [[microarchitecture::K6]]}} | ||

</table> | </table> | ||

| + | |||

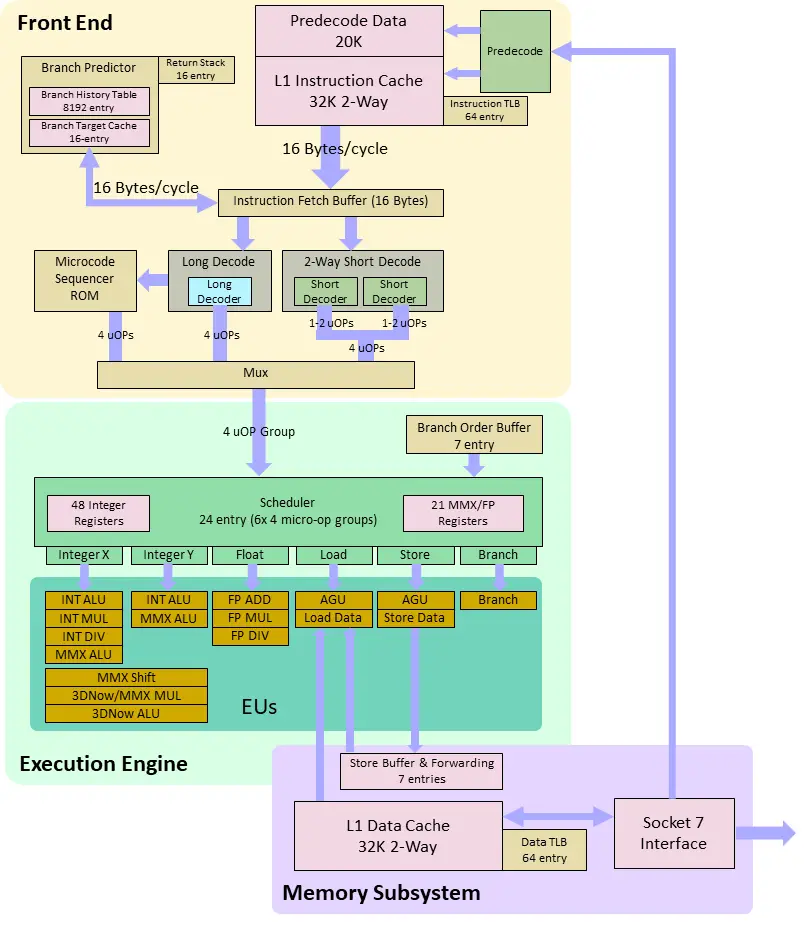

| + | == Block Diagram == | ||

| + | |||

| + | :[[File:K6 block diagram.png]] | ||

== See also == | == See also == | ||

| Line 102: | Line 148: | ||

== References == | == References == | ||

| − | * AMD K6-2 Data Sheet [http://www.amd-k6.com/wp-content/uploads/2012/07/AMD_K6-2_Desktop_Datasheet.pdf] | + | * AMD K6-2 Data Sheet: [http://www.amd-k6.com/wp-content/uploads/2012/07/AMD_K6-2_Desktop_Datasheet.pdf AMD K6-2 Desktop Datasheet] |

| − | * AMD K6 Code Optimization [http://www.ii.uib.no/~osvik/amd_opt/21924d.pdf] | + | * AMD K6 Code Optimization: [http://www.ii.uib.no/~osvik/amd_opt/21924d.pdf AMD K6 Code Optimization] |

Revision as of 11:00, 27 April 2025

| Edit Values | |

| K6 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | AMD, NexGen |

| Manufacturer | AMD |

| Introduction | April 2, 1997 |

| Phase-out | 2000 |

| Process | 350 nm, 250 nm |

| Instructions | |

| ISA | x86-32 |

| Succession | |

K6 was the microarchitecture for AMD's K6 line of microprocessors as a successor to the K5. Contrary to its namesake, K6 design is entirely NexGen's and not based on K5. Launched in early 1997, the K6 microarchitecture provided the superior performance AMD needed to become a viable competitor to Intel (performance K5 failed to deliver). K6 was superseded by K6-2 in 1998.

Contents

Architecture

- 6-7 stage integer pipeline

- Fetch

- Decode

- Micro-op issue

- Operand Fetch

- Execute 1

- Optional Execute 2

- Commit

- Branch Predictor

- 2-level predictor with 8192 entry branch history table

- Does not store target addresses. Target addresses are calculated during instruction decode

- 16-entry branch target cache

- Caches 16 bytes of instructions at the branch target, and supplies that directly

to the decoders to avoid a 1-cycle penalty

- Caches 16 bytes of instructions at the branch target, and supplies that directly

- 16-entry return address stack

- 2-level predictor with 8192 entry branch history table

- 32K 2-way L1 Instruction Cache

- Also holds 20K of predecode data. Instructions are predecoded as L1 instruction cache is filled

- 64 entry TLB

- Fetch and Decode

- 16 instruction bytes fetched per cycle, either from L1 instruction cache or branch target cache

- Decoders can handle the following combinations per clock:

- Short decode: Two x86 instructions that generate up to two micro-ops each

- Vector decode: One x86 instruction that generates up to four micro-ops

- Complex instructions handled by microcode

- Out of order execution resources

- Scheduler holds 6 groups of 4 micro-ops, or up to 12 x64 instructions

- Receives a group of 4 micro-ops from decoders every cycle. If fewer than 4 micro-ops are generated from the decoders, empty slots are padded with NOPs

- Retires one 4-micro-op group every cycle

- 48 integer registers: 8 architectural, 16 scratch, 24 rename

- 21 MMX registers: 8 architectural, 1 scratch, 12 rename

- Up to 7 outstanding branches

- 7 entry store queue

- Scheduler holds 6 groups of 4 micro-ops, or up to 12 x64 instructions

- Issues up to 6 micro-ops per cycle. Ports:

- Integer X: All ALU ops, including multiplies and divides

- Integer Y: Basic ALU ops

- Both integer pipelines can handle MMX/3DNow instructions, but share MMX/3DNow multiplier and MMX shifter functional units. If the two pipelines try to issue operations to a shared functional unit, one operation will stall.

- Floating point

- Load

- Store

- Branch

- 32K 2-way L1 Data Cache

- Dual ported, write back

- 128 entry TLB

- Load unit has 2-cycle latency

Am386/Am486/Am5x86/K5/K6/K7/K8

| Architecture | Process (nm) |

Family | Release date |

Code name | Model group | Cores | Clock rate (MHz) |

|---|---|---|---|---|---|---|---|

| K5 | 500 nm 350 nm |

AMD K5 | 1996 | SSA/5, 5k86 | 1 | 75–133 | |

| K6 | 350 nm 250 nm |

AMD K6 | 1997 1998 |

6k86 (NX686) Little Foot |

AMD-K6-166 ÷ 233 AMD-K6/233 ÷ 300 |

1 | 166–300 |

| 250 nm 180 nm |

AMD K6-2(+) | 1999 | Chomper (Extended, Mobile) |

K6-2 (Chompers/CXT) K6-2-P (Mobile K6-2) |

166–550 | ||

| AMD K6-III(+) | 2001 | Sharptooth | K6-III (Sharptooth) K6-III-P |

400–550 |

All K6 Chips

| K6 Chips | |||||

|---|---|---|---|---|---|

| Model | Core | Launched | Power Dissipation | Freq | Max Mem |

| AMD-K6-166ALR | 6k86 | May 1997 | 17.2 W 17,200 mW 0.0231 hp 0.0172 kW | 166.66 MHz 0.167 GHz 166,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6-166ALYD | 6k86 | May 1997 | 17.2 W 17,200 mW 0.0231 hp 0.0172 kW | 166.66 MHz 0.167 GHz 166,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6-200AFR | 6k86 | May 1997 | 20 W 20,000 mW 0.0268 hp 0.02 kW | 199.99 MHz 0.2 GHz 199,990 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6-200ALR | 6k86 | May 1997 | 20 W 20,000 mW 0.0268 hp 0.02 kW | 199.99 MHz 0.2 GHz 199,990 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6-200ALYD | 6k86 | May 1997 | 20 W 20,000 mW 0.0268 hp 0.02 kW | 199.99 MHz 0.2 GHz 199,990 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6-233AFR | 6k86 | May 1997 | 28.3 W 28,300 mW 0.038 hp 0.0283 kW | 233.33 MHz 0.233 GHz 233,330 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6-233ANR | 6k86 | May 1997 | 28.3 W 28,300 mW 0.038 hp 0.0283 kW | 233.33 MHz 0.233 GHz 233,330 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6-233APR | 6k86 | May 1997 | 28.3 W 28,300 mW 0.038 hp 0.0283 kW | 233.33 MHz 0.233 GHz 233,330 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/233ACZ | Little Foot | 5 March 1998 | 9 W 9,000 mW 0.0121 hp 0.009 kW | 233.33 MHz 0.233 GHz 233,330 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/233ADZ | Little Foot | 5 March 1998 | 9 W 9,000 mW 0.0121 hp 0.009 kW | 233.33 MHz 0.233 GHz 233,330 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/233BCZ | Little Foot | 5 March 1998 | 9 W 9,000 mW 0.0121 hp 0.009 kW | 233.33 MHz 0.233 GHz 233,330 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/266ACZ | Little Foot | 5 March 1998 | 9.8 W 9,800 mW 0.0131 hp 0.0098 kW | 266.66 MHz 0.267 GHz 266,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/266ADZ | Little Foot | 5 March 1998 | 9.8 W 9,800 mW 0.0131 hp 0.0098 kW | 266.66 MHz 0.267 GHz 266,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/266AFR | Little Foot | 5 March 1998 | 14.5 W 14,500 mW 0.0194 hp 0.0145 kW | 266.66 MHz 0.267 GHz 266,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/266BCZ | Little Foot | 5 March 1998 | 9.8 W 9,800 mW 0.0131 hp 0.0098 kW | 266.66 MHz 0.267 GHz 266,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/300ADZ | Little Foot | 5 March 1998 | 11 W 11,000 mW 0.0148 hp 0.011 kW | 299.99 MHz 0.3 GHz 299,990 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/300AFR | Little Foot | 5 March 1998 | 15.4 W 15,400 mW 0.0207 hp 0.0154 kW | 299.99 MHz 0.3 GHz 299,990 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/300BDZ | Little Foot | 5 March 1998 | 11 W 11,000 mW 0.0148 hp 0.011 kW | 299.99 MHz 0.3 GHz 299,990 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/PR2-166ALR | 6k86 | 2 April 1997 | 17.2 W 17,200 mW 0.0231 hp 0.0172 kW | 166.66 MHz 0.167 GHz 166,660 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| AMD-K6/PR2-200ALR | 6k86 | 2 April 1997 | 20 W 20,000 mW 0.0268 hp 0.02 kW | 199.99 MHz 0.2 GHz 199,990 kHz | 4,096 MiB 4,194,304 KiB 4,294,967,296 B 4 GiB 0.00391 TiB |

| Count: 20 | |||||

Block Diagram

See also

References

- AMD K6-2 Data Sheet: AMD K6-2 Desktop Datasheet

- AMD K6 Code Optimization: AMD K6 Code Optimization

Facts about "K6 - Microarchitectures - AMD"

| codename | K6 + |

| designer | AMD + and NexGen + |

| first launched | April 2, 1997 + |

| full page name | amd/microarchitectures/k6 + |

| instance of | microarchitecture + |

| instruction set architecture | x86-32 + |

| manufacturer | AMD + |

| microarchitecture type | CPU + |

| name | K6 + |

| phase-out | 2000 + |

| process | 350 nm (0.35 μm, 3.5e-4 mm) + and 250 nm (0.25 μm, 2.5e-4 mm) + |