From WikiChip

Difference between revisions of "samsung/exynos/3110"

| Line 25: | Line 25: | ||

|max cpus=1 | |max cpus=1 | ||

|max memory=512 MiB | |max memory=512 MiB | ||

| − | |||

| − | |||

| − | |||

| − | |||

|packaging=Yes | |packaging=Yes | ||

|package 0=FBGA | |package 0=FBGA | ||

Latest revision as of 20:28, 27 March 2018

| Edit Values | |

| Exynos 3110 | |

| General Info | |

| Designer | Samsung, ARM Holdings |

| Manufacturer | Samsung |

| Model Number | 3110 |

| Market | Mobile |

| Introduction | March 23, 2010 (announced) March 23, 2010 (launched) |

| General Specs | |

| Family | Exynos |

| Series | Exynos 3 |

| Frequency | 1,000 MHz |

| Bus type | AXI |

| Microarchitecture | |

| ISA | ARMv7 (ARM) |

| Microarchitecture | Cortex-A8 |

| Core Name | Cortex-A8 |

| Process | 45 nm |

| Technology | CMOS |

| Word Size | 32 bit |

| Cores | 1 |

| Threads | 1 |

| Max Memory | 512 MiB |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

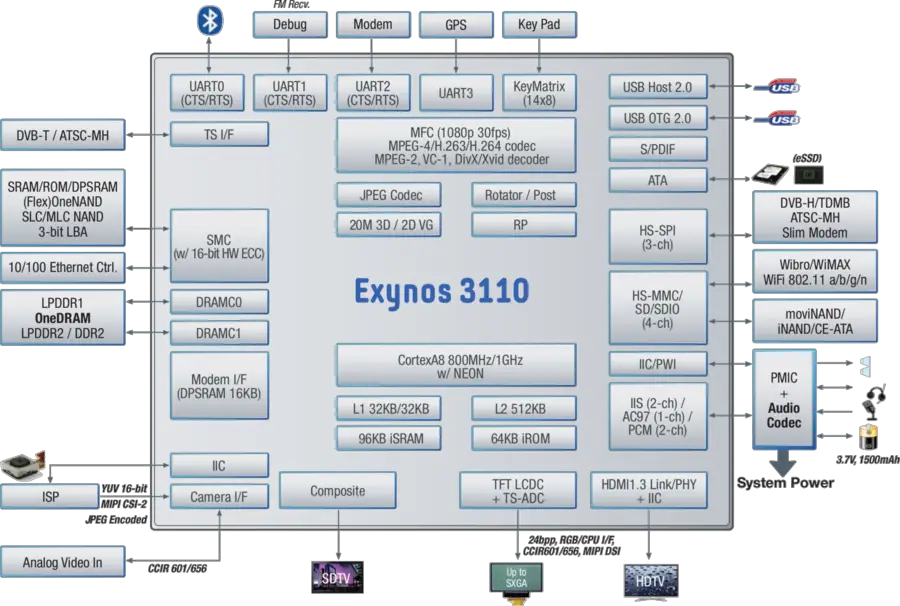

Exynos 3110 (formerly S5PC110) is a single-core 32-bit performance ARM system on a chip introduced by Samsung in 2010. The Exynos 3110 was the first model from the Exynos family which found its way into many of Samsung's and Google's devices including the Galaxy S line, Galaxy Tab, and the Nexus S. The Exynos 3110 incorporates a Cortex-A8 core operating at 1 GHz along with a PowerVR SGX540 IGP operating at 200 MHz. This SoC supports up to LPDDR2-400 dual-channel memory.

Contents

Cache[edit]

- Main article: Cortex-A8 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

- Flash: OneNAND 512MB

- Micro-SD slot (2GB bundle)

- Standard SDHC slot

Expansions[edit]

|

Expansion Options

|

||||||||||||

|

||||||||||||

Graphics[edit]

The PowerVR SGX540 is capable of up to 20M triangles/s and 1000M pixels/s.

|

Integrated Graphics Information

|

||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||

Wireless[edit]

- UMTS 850/1900/2100

- GSM 850/900/1800/1900MHz, HSPA+ up to 21.1 Mbps

| Wi-Fi | |||||||||

| WiFi |

| ||||||||

|---|---|---|---|---|---|---|---|---|---|

| Cellular | |||||||||

| 2G |

| ||||||||

| 3G |

| ||||||||

Features[edit]

[Edit/Modify Supported Features]

|

Supported ARM Extensions & Processor Features

|

||||||

|

||||||

Utilizing devices[edit]

- Samsung Galaxy SL

- Samsung Galaxy S

- Samsung Galaxy S Vibrant

- Samsung Galaxy S

- Samsung Wave S8500

- Samsung Wave II S8530

- Samsung Galaxy Tab

- Samsung Droid Charge

- Samsung Exhibit 4G

- Samsung Stratosphere

- Google Nexus S

- Meizu M9

This list is incomplete; you can help by expanding it.

Diagram[edit]

Documents[edit]

Datasheets[edit]

Facts about "Exynos 3110 - Samsung"

| base frequency | 1,000 MHz (1 GHz, 1,000,000 kHz) + |

| bus type | AXI + |

| core count | 1 + |

| core name | Cortex-A8 + |

| designer | Samsung + and ARM Holdings + |

| family | Exynos + |

| first announced | March 23, 2010 + |

| first launched | March 23, 2010 + |

| former name | S5PC110 + |

| full page name | samsung/exynos/3110 + |

| has 2g support | true + |

| has 3g support | true + |

| has ecc memory support | false + |

| has gprs support | true + |

| has gsm support | true + |

| has hsdpa support | true + |

| has umts support | true + |

| instance of | microprocessor + |

| integrated gpu | PowerVR SGX540 + |

| integrated gpu base frequency | 400 MHz (0.4 GHz, 400,000 KHz) + |

| integrated gpu designer | Imagination Technologies + |

| integrated gpu execution units | 1 + |

| integrated gpu max memory | 512 MiB (524,288 KiB, 536,870,912 B, 0.5 GiB) + |

| isa | ARMv7 + |

| isa family | ARM + |

| l1$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l1d$ size | 32 KiB (32,768 B, 0.0313 MiB) + |

| l1i$ size | 32 KiB (32,768 B, 0.0313 MiB) + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| ldate | March 23, 2010 + |

| manufacturer | Samsung + |

| market segment | Mobile + |

| max cpu count | 1 + |

| max memory | 512 MiB (524,288 KiB, 536,870,912 B, 0.5 GiB, 4.882812e-4 TiB) + |

| max memory bandwidth | 5.96 GiB/s (6,103.04 MiB/s, 6.4 GB/s, 6,399.501 MB/s, 0.00582 TiB/s, 0.0064 TB/s) + |

| max memory channels | 2 + |

| microarchitecture | Cortex-A8 + |

| model number | 3110 + |

| name | Exynos 3110 + |

| process | 45 nm (0.045 μm, 4.5e-5 mm) + |

| series | Exynos 3 + |

| smp max ways | 1 + |

| supported memory type | LPDDR2-400 + |

| technology | CMOS + |

| thread count | 1 + |

| used by | Samsung Galaxy SL +, Samsung Galaxy S +, Samsung Galaxy S Vibrant +, Samsung Wave S8500 +, Samsung Wave II S8530 +, Samsung Galaxy Tab +, Samsung Droid Charge +, Samsung Exhibit 4G +, Samsung Stratosphere +, Google Nexus S + and Meizu M9 + |

| word size | 32 bit (4 octets, 8 nibbles) + |