From WikiChip

Difference between revisions of "loongson/godson 2/2g"

| Line 91: | Line 91: | ||

'''Godson-2G''' is a {{arch|64}} [[MIPS]] performance processor developed by [[Institute of Computing Technology of the Chinese Academy of Sciences|ICT]] and later [[Loongson]] for desktop computers. Introduced in late-[[2010]], the Godson-2G operates at up to 1 GHz consuming up to 4 W. This chip was manufactured on [[STMicroelectronics]]' [[65 nm process]]. | '''Godson-2G''' is a {{arch|64}} [[MIPS]] performance processor developed by [[Institute of Computing Technology of the Chinese Academy of Sciences|ICT]] and later [[Loongson]] for desktop computers. Introduced in late-[[2010]], the Godson-2G operates at up to 1 GHz consuming up to 4 W. This chip was manufactured on [[STMicroelectronics]]' [[65 nm process]]. | ||

| − | This specific models incorporates a considerably larger [[2nd level cache]] compared to the rest of the {{\\\|Godson 2}} family along with an extended number of additional interfaces in a relatively large package. | + | This specific models incorporates a considerably larger [[2nd level cache]] compared to the rest of the {{\\\|Godson 2}} family along with an extended number of additional interfaces in a relatively large package. The Godson-2G integrates the majority of the [[southbridge]] on-die. |

== Cache == | == Cache == | ||

Revision as of 02:33, 19 March 2017

Template:mpu Godson-2G is a 64-bit MIPS performance processor developed by ICT and later Loongson for desktop computers. Introduced in late-2010, the Godson-2G operates at up to 1 GHz consuming up to 4 W. This chip was manufactured on STMicroelectronics' 65 nm process.

This specific models incorporates a considerably larger 2nd level cache compared to the rest of the Godson 2 family along with an extended number of additional interfaces in a relatively large package. The Godson-2G integrates the majority of the southbridge on-die.

Cache

- Main article: GS464 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions

This chip has integrated HyperTransport 1.0 operating at 400 MHz.

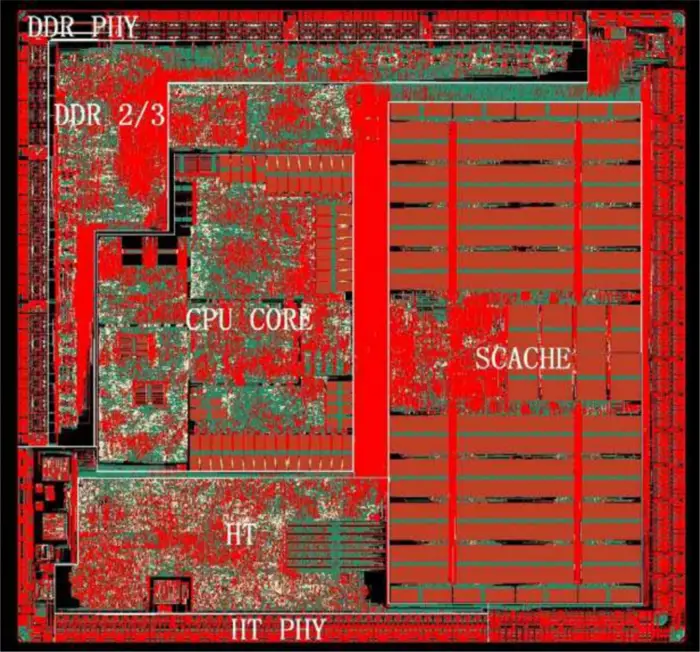

Die Shot

- 65 nm process

- 100,000,000 transistors

- 53.54 mm² die size

References

- Zhao, Ji-Ye, et al. "Physical Design Methodology for Godson-2G Microprocessor." Journal of Computer Science and Technology 25.2 (2010): 225-231.

- Weiwu Hu, Yunji Chen, "GS464V: A High-Performance Low-Power XPU with 512-Bit Vector Extension", HotChips 22 (2010).

Facts about "Godson-2G - Loongson"

| has ecc memory support | true + |

| l1$ size | 128 KiB (131,072 B, 0.125 MiB) + |

| l1d$ description | 4-way set associative + |

| l1d$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l2$ description | 4-way set associative + |

| l2$ size | 1 MiB (1,024 KiB, 1,048,576 B, 9.765625e-4 GiB) + |

| max memory bandwidth | 11.92 GiB/s (12,206.08 MiB/s, 12.799 GB/s, 12,799.003 MB/s, 0.0116 TiB/s, 0.0128 TB/s) + |

| max memory channels | 1 + |

| supported memory type | DDR3-800 + |