From WikiChip

Difference between revisions of "intel/core i7ee/i7-5960x"

| Line 68: | Line 68: | ||

| socket type = LGA | | socket type = LGA | ||

}} | }} | ||

| − | The '''Core i7-5960X {{intel|Core i7EE|Extreme Edition}}''' is a {{arch|64}} octa-core top-of-the-line [[MPU]] introduced by [[Intel]] for the enthusiasts market. The i7-5960X replaces the {{\\|i7-4960X}}, as Intel's flagship microprocessor based on {{intel|Haswell}} microarchitecture - also becoming the first consumer-class octa-core microprocessor. This chip operates at 3 GHz with turbo frequency of up to 3.5 GHz for a single core. The i7-5960X supports up to 64 GB of memory (DDR4). | + | The '''Core i7-5960X {{intel|Core i7EE|Extreme Edition}}''' is a {{arch|64}} octa-core top-of-the-line [[MPU]] introduced by [[Intel]] for the enthusiasts market in mid-[[2014]]. The i7-5960X replaces the {{\\|i7-4960X}}, as Intel's flagship microprocessor based on {{intel|Haswell}} microarchitecture - also becoming the first consumer-class octa-core microprocessor. This chip operates at 3 GHz with turbo frequency of up to 3.5 GHz for a single core. The i7-5960X supports up to 64 GB of memory (DDR4). This processor was eventually replaced by {{\\|i7-6950X}}, a {{intel|Broadwell}}-based model. |

== Cache == | == Cache == | ||

Revision as of 17:03, 9 September 2016

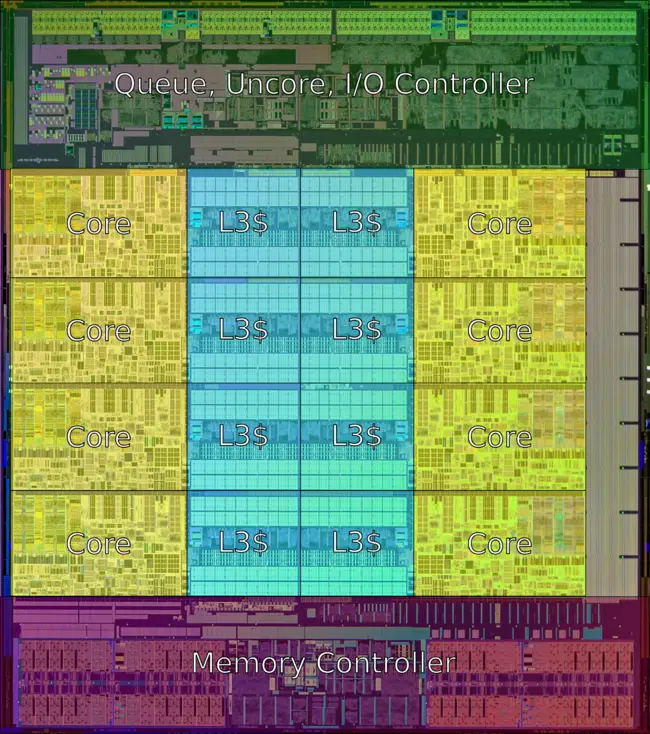

Template:mpu The Core i7-5960X Extreme Edition is a 64-bit octa-core top-of-the-line MPU introduced by Intel for the enthusiasts market in mid-2014. The i7-5960X replaces the i7-4960X, as Intel's flagship microprocessor based on Haswell microarchitecture - also becoming the first consumer-class octa-core microprocessor. This chip operates at 3 GHz with turbo frequency of up to 3.5 GHz for a single core. The i7-5960X supports up to 64 GB of memory (DDR4). This processor was eventually replaced by i7-6950X, a Broadwell-based model.

Cache

- Main article: Haswell's Cache

| Cache Info [Edit Values] | ||

| L1I$ | 256 KB "KB" is not declared as a valid unit of measurement for this property. |

8x32 KB 8-way set associative (per core) |

| L1D$ | 256 KB "KB" is not declared as a valid unit of measurement for this property. |

8x32 KB 8-way set associative (per core) |

| L2$ | 2 MB "MB" is not declared as a valid unit of measurement for this property. |

8x256 KB 8-way set associative (per core) |

| L3$ | 20 MB "MB" is not declared as a valid unit of measurement for this property. |

8x2.5 20-way set associative (shared) |

Graphics

This SoC has no integrated graphics processing unit.

Memory controller

| Integrated Memory Controller | |

| Type | DDR4-1600, DDR4-1866, DDR4-2133 |

| Controllers | 1 |

| Channels | 4 |

| ECC Support | No |

| Max bandwidth | 68 GB/s |

| Max memory | 64 GB |

Expansions

Features

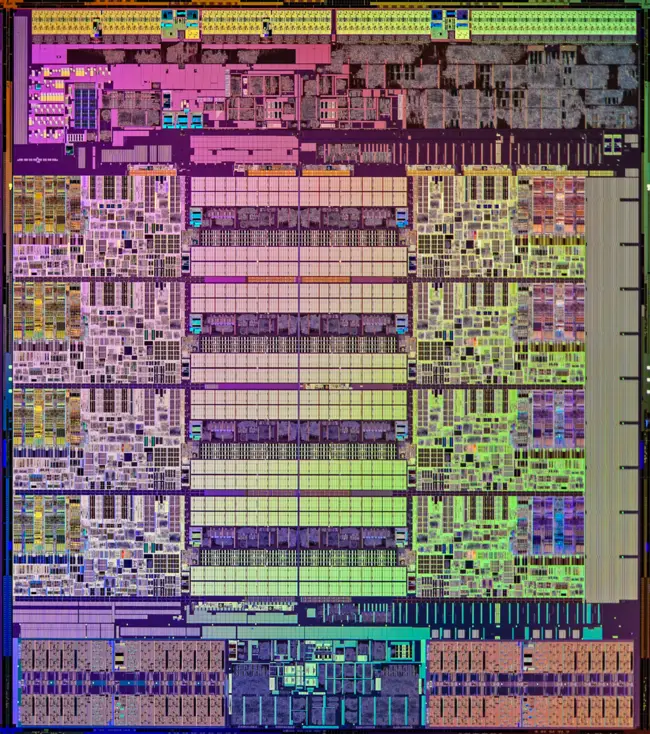

Die Shot

- 2,600,000,000 transistors

- 355.52 mm2

- 17.6 mm x 20.2 mm

See also

Facts about "Core i7-5960X Extreme Edition - Intel"

| l1d$ description | 8-way set associative + |

| l1i$ description | 8-way set associative + |

| l2$ description | 8-way set associative + |

| l3$ description | 20-way set associative + |