(→Members) |

(→Object) |

||

| Line 38: | Line 38: | ||

=== Object === | === Object === | ||

There are five different types of components: [[Arithmetic Logic Unit]] (ALU), [[Content Addressable Memory]] (CAM), [[Cyclic Redundancy Check]] (CRC), [[Multiply Accumulator]] (MAC), and [[Register File]] (RF). The control program guides the overall program execution and the datapath setup. Datapath is {{arch|16}} but may be combined with adjacent objects to [[bit-slice microprocessor|form larger datapaths]] of desired size. | There are five different types of components: [[Arithmetic Logic Unit]] (ALU), [[Content Addressable Memory]] (CAM), [[Cyclic Redundancy Check]] (CRC), [[Multiply Accumulator]] (MAC), and [[Register File]] (RF). The control program guides the overall program execution and the datapath setup. Datapath is {{arch|16}} but may be combined with adjacent objects to [[bit-slice microprocessor|form larger datapaths]] of desired size. | ||

| + | |||

| + | * [[arithmetic logic unit|ALU]] | ||

| + | ** {{arch|16}} add/sub/shift/rotate/AND/OR/XOR | ||

| + | ** circuitry for cascading status bits for making larger word | ||

| + | * [[truth function]] | ||

| + | ** 4x 4:1 [[lookup table]]s | ||

| + | * [[multiply accumulator|MAC]] | ||

| + | ** 16x16 single clock cycle [[multiplier]] | ||

| + | ** 40-bit [[accumulator]] | ||

| + | * [[register file|RF]] | ||

| + | ** 320 Bytes | ||

| + | ** Configurable 20 or 40-bit data | ||

| + | ** Two modes: | ||

| + | *** Dual-ported RAM, single-cycle access | ||

| + | *** Single-cycle FIFO | ||

| + | * [[crc unit|CRC]] | ||

| + | ** 16x 20-bit patterns | ||

| + | ** 20-bit result | ||

| + | ** output feedback | ||

| + | * Internal Block [[RAM]] | ||

| + | ** 1024x76b (9KB) | ||

{{clear}} | {{clear}} | ||

| + | |||

== Members == | == Members == | ||

The amount and types of the individual objects were chosen based on the applications the were meant to run on the chip. MathStar divided the product line into BridgeBuilder, FilterBuilder, StorageBuilder, SecurityBuilder and SwitchBuilder. | The amount and types of the individual objects were chosen based on the applications the were meant to run on the chip. MathStar divided the product line into BridgeBuilder, FilterBuilder, StorageBuilder, SecurityBuilder and SwitchBuilder. | ||

Revision as of 15:35, 27 June 2016

| Builder | |

| Developer | MathStar |

| Manufacturer | TSMC |

| Type | Programmable logic device |

| Introduction | 2002 (announced) 2003 (launch) |

| Production | 2003-2005 |

| Word size | 16 bit 2 octets

4 nibbles |

| Process | 130 nm 0.13 μm

1.3e-4 mm |

| Technology | CMOS |

| Clock | 100 MHz-1,000 MHz |

| Succession | |

| → | |

| Arrix | |

Builder was a family of FPOAs introduced by MathStar in 2003. This family the earliest attempt at designing an FPOA and was discontinued shortly after due to some technical issues. The Builder family was phased out entirely by 2005.

Contents

Architecture

- Main article: field-programmable object array

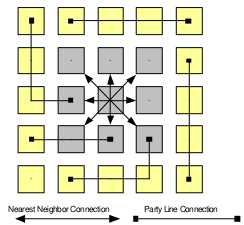

The Builder family was the MathStar's initial attempt at a field-programmable object array. Each chip contains 100s of silicon objects laid out in a grid, broken down to arrays of five objects each. Instructions are loaded to each of the objects at power-up.

Inter-Object communication was done primarily by passing data to the nearest neighbor through a unidirectional synchronous interconnect. Communication is configured dynamically and on-demand. Each object had the facilities needed for clock synchronization, built-in self-test, etc...

Object

There are five different types of components: Arithmetic Logic Unit (ALU), Content Addressable Memory (CAM), Cyclic Redundancy Check (CRC), Multiply Accumulator (MAC), and Register File (RF). The control program guides the overall program execution and the datapath setup. Datapath is 16-bit but may be combined with adjacent objects to form larger datapaths of desired size.

- ALU

- 16-bit add/sub/shift/rotate/AND/OR/XOR

- circuitry for cascading status bits for making larger word

- truth function

- 4x 4:1 lookup tables

- MAC

- 16x16 single clock cycle multiplier

- 40-bit accumulator

- RF

- 320 Bytes

- Configurable 20 or 40-bit data

- Two modes:

- Dual-ported RAM, single-cycle access

- Single-cycle FIFO

- CRC

- 16x 20-bit patterns

- 20-bit result

- output feedback

- Internal Block RAM

- 1024x76b (9KB)

Members

The amount and types of the individual objects were chosen based on the applications the were meant to run on the chip. MathStar divided the product line into BridgeBuilder, FilterBuilder, StorageBuilder, SecurityBuilder and SwitchBuilder.

BridgeBuilder

The BridgeBuilder series was designed for high-speed networking applications handling 10Gbps or more as well as bus bridging applications.

FilterBuilder

The FilterBuilder series was designed for filter applications (high performance FFTs and FIRs).

StorageBuilder

The FilterBuilder series was aimed to be combined with MathStar's network offload engine.

SecurityBuilder

The SecurityBuilder series was designed for various security applications with libraries that implement custom versions of security protocols at up to 10Gbps throughput.

SwitchBuilder

The SwitchBuilder series was designed for high-performance switching/networking applications such as for PCI-Express, Fibre Channel, Ethernet, RapidIO and others.

| designer | MathStar + |

| first announced | 2002 + |

| first launched | 2003 + |

| full page name | mathstar/builder + |

| instance of | integrated circuit family + |

| main designer | MathStar + |

| manufacturer | TSMC + |

| name | Builder + |

| process | 130 nm (0.13 μm, 1.3e-4 mm) + |

| technology | CMOS + |

| word size | 16 bit (2 octets, 4 nibbles) + |