From WikiChip

Difference between revisions of "amd/packages/sp1"

(Created page with "{{amd title|Package SP1}} {{package |name=SP1 |designer=AMD |market=Server |market 2=Embedded |first announced=January 2014 |first launched=January 2016 |microarch=Cortex-A57...") |

(fixed) |

||

| (2 intermediate revisions by one other user not shown) | |||

| Line 1: | Line 1: | ||

{{amd title|Package SP1}} | {{amd title|Package SP1}} | ||

{{package | {{package | ||

| − | |name=SP1 | + | |name=Package SP1 |

|designer=AMD | |designer=AMD | ||

|market=Server | |market=Server | ||

| Line 14: | Line 14: | ||

|package dimension=27 mm | |package dimension=27 mm | ||

|package dimension 2=27 mm | |package dimension 2=27 mm | ||

| − | |package pitch=0.65 | + | |package pitch=0.65 mm |

}} | }} | ||

| − | '''SP1''' was a '''BGA-1021''' package for [[AMD]] server microprocessors codenamed {{ | + | '''Package SP1''' was a '''BGA-1021''' package for [[AMD]] server microprocessors codenamed {{amd|Seattle|l=core}} |

| + | :with 8x ARM {{armh|Cortex-A57|l=arch}} CPU cores. | ||

| + | * [[amd/List of AMD CPU sockets|List of AMD CPU sockets]] | ||

=== Features === | === Features === | ||

| Line 25: | Line 27: | ||

likely a multi-pitch minimum. --> | likely a multi-pitch minimum. --> | ||

* 1021-pin lidless micro ball grid array package, 0.65 mm pitch minimum, 27 × 27 mm, organic substrate | * 1021-pin lidless micro ball grid array package, 0.65 mm pitch minimum, 27 × 27 mm, organic substrate | ||

| − | + | * 2× 64/72 bit DDR3 SDRAM interface up to 800 MHz, PC3-12800 (DDR3-1600), 25.6 GB/s or | |

| − | * | + | * 2× 64/72 bit DDR4 SDRAM interface up to 933 MHz, PC4-14900 (DDR4-1866), 29.9 GB/s |

| − | * | ||

** Up to 4 UDIMMs, RDIMMs, or SODIMMs (2 per channel), ECC supported | ** Up to 4 UDIMMs, RDIMMs, or SODIMMs (2 per channel), ECC supported | ||

** Up to 128 GB total with RDIMMs | ** Up to 128 GB total with RDIMMs | ||

| Line 35: | Line 36: | ||

* Integrated Controller Hub | * Integrated Controller Hub | ||

| − | ** | + | ** 14× SATA 1.0, 2.0, 3.0 (6 Gb/s) |

| − | ** | + | ** 2× 10 Gigabit Ethernet |

** 1 GbE system management port | ** 1 GbE system management port | ||

** SPI, UART, I2C, GPIO | ** SPI, UART, I2C, GPIO | ||

== Processors using SP1 == | == Processors using SP1 == | ||

| − | * AMD Opteron A1100 Series | + | * [[AMD]] [[Opteron]] A1100 Series |

<!-- NOTE: | <!-- NOTE: | ||

Latest revision as of 07:48, 15 May 2025

| Edit Values | |

| Package SP1 | |

| General Info | |

| Designer | AMD |

| Introduction | January 2014 (announced) January 2016 (launched) |

| Market | Server, Embedded |

| Microarchitecture | Cortex-A57 |

| TDP | 32 W 32,000 mW 0.0429 hp 0.032 kW |

| Package | |

| Name | BGA-1021 |

| Type | Organic Micro Ball Grid Array |

| Contacts | 1021 |

| Dimension | 27 mm 2.7 cm × 27 mm1.063 in 2.7 cm 1.063 in |

| Pitch | 0.65 mm 0.0256 in |

Package SP1 was a BGA-1021 package for AMD server microprocessors codenamed Seattle

- with 8x ARM Cortex-A57 CPU cores.

Features[edit]

- 1021-pin lidless micro ball grid array package, 0.65 mm pitch minimum, 27 × 27 mm, organic substrate

- 2× 64/72 bit DDR3 SDRAM interface up to 800 MHz, PC3-12800 (DDR3-1600), 25.6 GB/s or

- 2× 64/72 bit DDR4 SDRAM interface up to 933 MHz, PC4-14900 (DDR4-1866), 29.9 GB/s

- Up to 4 UDIMMs, RDIMMs, or SODIMMs (2 per channel), ECC supported

- Up to 128 GB total with RDIMMs

- PCIe Gen 1.0, 2.0, 3.0 (8 GT/s)

- 8 lanes configurable 1x8, 2x4, 1x4 + 2x2

- Integrated Controller Hub

- 14× SATA 1.0, 2.0, 3.0 (6 Gb/s)

- 2× 10 Gigabit Ethernet

- 1 GbE system management port

- SPI, UART, I2C, GPIO

Processors using SP1[edit]

| List of all SP1-based Processors | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Model | Price | Process | Launched | µarch | Family | Core | C | T | Freq | Turbo | TDP | ||||||||

| Count: 0 | |||||||||||||||||||

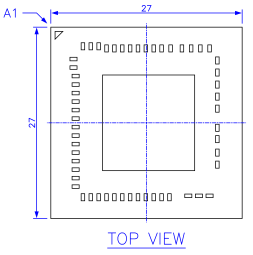

Package Diagram[edit]

Approximate dimensions of the Seattle package, Part No. 31667. All dimensions in millimeters.

Pin Map[edit]

No data available.

References[edit]

- "Product Brief: AMD Opteron™ A1100 SOC Series", PID 158465-B, 2016

- "Hot Chips 26: The AMD Opteron™ A1100 Processor Codenamed "Seattle"", August 11, 2014

- "Introducing the AMD Opteron™ A1100 for the Datacenter", January 2016

Facts about "Package SP1 - AMD"

| designer | AMD + |

| first announced | January 2014 + |

| first launched | January 2016 + |

| instance of | package + |

| market segment | Server + and Embedded + |

| microarchitecture | Cortex-A57 + |

| name | SP1 + |

| package | BGA-1021 + |

| package contacts | 1,021 + |

| package length | 27 mm (2.7 cm, 1.063 in) + |

| package type | Organic Micro Ball Grid Array + |

| package width | 27 mm (2.7 cm, 1.063 in) + |

| tdp | 32 W (32,000 mW, 0.0429 hp, 0.032 kW) + |