From WikiChip

Difference between revisions of "ibm/power/02cy296"

(→Expansions) |

|||

| (One intermediate revision by the same user not shown) | |||

| Line 36: | Line 36: | ||

}} | }} | ||

'''POWER9 02CY296''' is a [[22-core]] [[POWER]] server and workstation microprocessor designed by [[IBM]] and introduced in late [[2017]]. This chip is based on the {{ibm|POWER9|l=arch}} microarchitecture and is fabricated on GlobalFoundries [[14 nm process|14nm SOI Process]]. The 02CY296 has a base frequency of 2.75 GHz with a bost frequency of 3.80 GHz and a TDP of 190 W. | '''POWER9 02CY296''' is a [[22-core]] [[POWER]] server and workstation microprocessor designed by [[IBM]] and introduced in late [[2017]]. This chip is based on the {{ibm|POWER9|l=arch}} microarchitecture and is fabricated on GlobalFoundries [[14 nm process|14nm SOI Process]]. The 02CY296 has a base frequency of 2.75 GHz with a bost frequency of 3.80 GHz and a TDP of 190 W. | ||

| + | |||

| + | == Cache == | ||

| + | {{main|ibm/microarchitectures/power9#Memory_Hierarchy|l1=POWER9 § Cache}} | ||

| + | {{cache size | ||

| + | |l1 cache=1.375 MiB | ||

| + | |l1i cache=704 KiB | ||

| + | |l1i break=22x32 KiB | ||

| + | |l1i desc=8-way set associative | ||

| + | |l1d cache=704 KiB | ||

| + | |l1d break=22x32 KiB | ||

| + | |l1d desc=8-way set associative | ||

| + | |l2 cache=5.5 MiB | ||

| + | |l2 break=11x512 KiB | ||

| + | |l2 desc=8-way set associative | ||

| + | |l3 cache=110 MiB | ||

| + | |l3 break=11x10 MiB | ||

| + | |l3 desc=20-way set associative | ||

| + | }} | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=DDR4-2666 | ||

| + | |ecc=No | ||

| + | |max mem=2 TiB | ||

| + | |controllers=2 | ||

| + | |channels=8 | ||

| + | |max bandwidth=158.95 GiB/s | ||

| + | |bandwidth schan=19.87 GiB/s | ||

| + | |bandwidth dchan=39.74 GiB/s | ||

| + | |bandwidth qchan=79.47 GiB/s | ||

| + | |bandwidth ochan=158.95 GiB/s | ||

| + | }} | ||

| + | |||

| + | {{ibm power9 sforza memory configs}} | ||

| + | |||

| + | == Expansions == | ||

| + | {{expansions main | ||

| + | | | ||

| + | {{expansions entry | ||

| + | |type=PCIe | ||

| + | |pcie revision=4.0 | ||

| + | |pcie lanes=48 | ||

| + | |pcie config=x16 | ||

| + | |pcie config 2=x8 | ||

| + | |pcie config 3=x4 | ||

| + | }} | ||

| + | }} | ||

| + | |||

| + | == Die == | ||

| + | {{see also|ibm/microarchitectures/power9#Die|l1=POWER9 § Die}} | ||

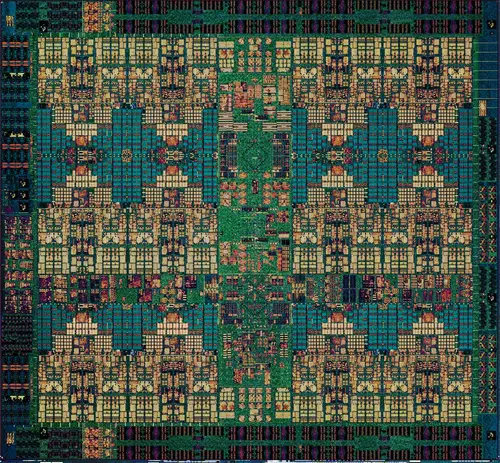

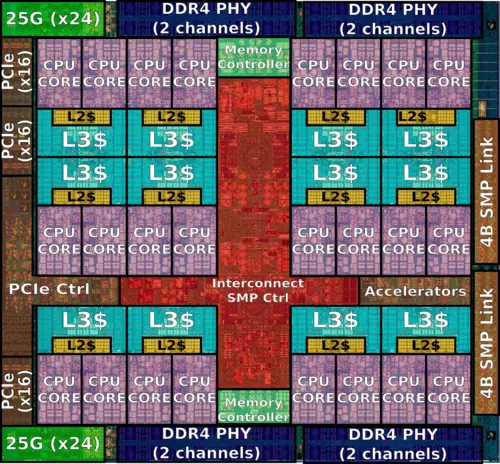

| + | A die shot of IBM's [[22-core]] server microprocessor used in this part: | ||

| + | |||

| + | : [[File:power9 so die.png|500px]] | ||

| + | |||

| + | |||

| + | : [[File:power9 so die (annotated).png|500px]] | ||

Latest revision as of 02:53, 17 January 2019

| Edit Values | |

| 02CY296 | |

| General Info | |

| Designer | IBM |

| Manufacturer | GlobalFoundries |

| Model Number | 02CY296 |

| Part Number | 02CY296 |

| Market | Server, Workstation |

| Introduction | November, 2017 (announced) November, 2017 (launched) |

| General Specs | |

| Family | POWER |

| Series | POWER9 |

| Frequency | 2.75 GHz |

| Turbo Frequency | 3.80 GHz |

| Microarchitecture | |

| ISA | Power ISA v3.0B (Power ISA) |

| Microarchitecture | POWER9 |

| Core Name | Sforza |

| Process | 14 nm |

| Transistors | 8,000,000,000 |

| Technology | CMOS |

| Die | 693.37 mm² 25.228 mm × 27.48416 mm |

| Word Size | 64 bit |

| Cores | 22 |

| Threads | 88 |

| Max Memory | 2 TiB |

| Multiprocessing | |

| Max SMP | 2-Way (Multiprocessor) |

| Electrical | |

| TDP | 190 W |

| Tjunction | 0 °C – 85 °C |

| Packaging | |

| Package | FCLGA-2601 (PLGA) |

| Dimension | 50 mm × 50 mm |

| Pitch | 1.016 mm |

| Contacts | 2601 |

POWER9 02CY296 is a 22-core POWER server and workstation microprocessor designed by IBM and introduced in late 2017. This chip is based on the POWER9 microarchitecture and is fabricated on GlobalFoundries 14nm SOI Process. The 02CY296 has a base frequency of 2.75 GHz with a bost frequency of 3.80 GHz and a TDP of 190 W.

Contents

Cache[edit]

- Main article: POWER9 § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

| [Edit] Memory Configurations | |

|---|---|

| Configuration | Speed |

| One DIMM per channel | 2666 MHz |

| Two DIMMs per channel | 2400 MHz |

Expansions[edit]

Expansion Options |

|||||

|

|||||

Die[edit]

- See also: POWER9 § Die

A die shot of IBM's 22-core server microprocessor used in this part:

Facts about "POWER9 02CY296 - IBM"

| full page name | ibm/power/02cy296 + |

| instance of | microprocessor + |

| ldate | 1900 + |