From WikiChip

Difference between revisions of "intel/80486/486dx4-100"

m (Bot: moving all {{mpu}} to {{chip}}) |

|||

| (13 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

{{intel title|i486DX4-100}} | {{intel title|i486DX4-100}} | ||

| − | {{ | + | {{chip |

| name = Intel i486DX4-100 | | name = Intel i486DX4-100 | ||

| − | + | | image = I486DX4.jpg | |

| − | | image = | ||

| image size = | | image size = | ||

| − | | caption = | + | | caption = A80486DX4-100, S-Spec SX900 |

| designer = Intel | | designer = Intel | ||

| manufacturer = Intel | | manufacturer = Intel | ||

| Line 38: | Line 37: | ||

| s-spec 6 = SX900 | | s-spec 6 = SX900 | ||

| s-spec 7 = SX908 | | s-spec 7 = SX908 | ||

| + | | s-spec 8 = SK053 | ||

| + | | s-spec 9 = SK063 | ||

| + | | s-spec 10 = SK099 | ||

| + | | s-spec 11 = SL2M9 | ||

| + | | s-spec 12 = SX876 | ||

| + | | s-spec 13 = SX906 | ||

| s-spec es = | | s-spec es = | ||

| − | | s-spec qs | + | | s-spec qs 2 = Q0746 |

| + | | s-spec qs 3 = Q0747 | ||

| + | | s-spec qs 4 = Q860 | ||

| cpuid = 480 | | cpuid = 480 | ||

| − | | cpuid | + | | cpuid 2 = 483 |

| microarch = 80486 | | microarch = 80486 | ||

| Line 57: | Line 64: | ||

| core count = 1 | | core count = 1 | ||

| max cpus = 1 | | max cpus = 1 | ||

| − | | max memory = 4 | + | | max memory = 4 GiB |

| + | |||

| − | |||

| power = 3.55 W | | power = 3.55 W | ||

| v core = 3.3 V | | v core = 3.3 V | ||

| Line 81: | Line 88: | ||

== Cache == | == Cache == | ||

{{main|intel/microarchitectures/80486#Memory_Hierarchy|l1=80486 § Cache}} | {{main|intel/microarchitectures/80486#Memory_Hierarchy|l1=80486 § Cache}} | ||

| + | The i486dx4-100 was offered with two cache policies. Models that came with a write-back cache were marked by an "'''&EW'''" identifier. Models that came with a write-through policy were marked by "'''&E'''". | ||

{{cache info | {{cache info | ||

| − | |l1 cache=16 | + | |l1 cache=16 KiB |

| − | |l1 break=1x16 | + | |l1 break=1x16 KiB |

|l1 desc=4-way set associative | |l1 desc=4-way set associative | ||

| − | |l1 extra=(unified, write-through policy) | + | |l1 extra=(unified, write-through/write-back policy) |

}} | }} | ||

| Line 93: | Line 101: | ||

== Features == | == Features == | ||

* {{intel|System Management Mode}} (SMM) | * {{intel|System Management Mode}} (SMM) | ||

| + | |||

| + | == Gallery == | ||

| + | <gallery> | ||

| + | Ic-photo-Intel--A80486DX4100-(486DX4-CPU).png|A80486DX4100, S-Spec SK096 | ||

| + | Ic-photo-intel-A80486DX4100-(486DX4).png|A80486DX4100, S-Spec SK096 | ||

| + | File:Intel DX4 microprocessor.jpg|A80486DX4100, S-Spec SK096 | ||

| + | File:Intel i486 DX4 100 MHz SK051.jpeg|A80486DX4100, S-Spec SK051 | ||

| + | File:Intel i486 DX4 100 SK051.jpg|A80486DX4100, S-Spec SK051 | ||

| + | </gallery> | ||

== See also == | == See also == | ||

* {{intel|80486|80486 family}} | * {{intel|80486|80486 family}} | ||

Latest revision as of 15:13, 13 December 2017

| Edit Values | |

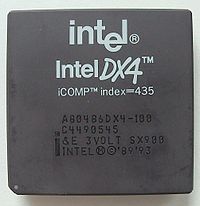

| Intel i486DX4-100 | |

| |

| A80486DX4-100, S-Spec SX900 | |

| General Info | |

| Designer | Intel |

| Manufacturer | Intel |

| Model Number | i486DX4-100 |

| Part Number | A80486DX4-100, A80486DX4WB100, MA80486DX4-100, TQ80486DX4100, MQ80486DX4-100, MQ80486DX4100, FC80486DX4-100, FC80486DX4WB100 |

| S-Spec | SK050, SK051, SK096, SK851, SX877, SX900, SX908, SK053, SK063, SK099, SL2M9, SX876, SX906 |

| Introduction | March 7, 1994 (launched) |

| Shop | Amazon |

| General Specs | |

| Family | 80486 |

| Series | 486DX4 |

| Frequency | 100 MHz |

| Bus type | FSB |

| Bus speed | 33 MHz |

| Bus rate | 33 MT/s |

| Clock multiplier | 3 |

| CPUID | 480, 483 |

| Microarchitecture | |

| Microarchitecture | 80486 |

| Core Name | 486DX4 |

| Process | 600 nm |

| Transistors | 1,600,000 |

| Technology | CMOS |

| Word Size | 32 bit |

| Cores | 1 |

| Max Memory | 4 GiB |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| Power dissipation | 3.55 W |

| Vcore | 3.3 V ± 0.3 V |

| OP Temperature | 0 °C – 85 °C |

i486DX4-100 was a fourth-generation x86 microprocessor introduced by Intel in 1994. This chip, which is based on the 80486 microarchitecture, had a clock multiplier of x2, x2.5, and x3 with a max operating frequency of 100 MHz, three times the bus frequency. Like the original i486DX, this chip implemented the 80387 FPU on-die and incorporated System Management Mode (SMM). The DX4 series had twice as much cache space as the older processors.

Contents

Cache[edit]

- Main article: 80486 § Cache

The i486dx4-100 was offered with two cache policies. Models that came with a write-back cache were marked by an "&EW" identifier. Models that came with a write-through policy were marked by "&E".

| Cache Info [Edit Values] | ||

| L1$ | 16 KiB 16,384 B 0.0156 MiB |

1x16 KiB 4-way set associative (unified, write-through/write-back policy) |

Graphics[edit]

This chip had no integrated graphics processing unit.

Features[edit]

- System Management Mode (SMM)